Simulating the design example – Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 13

Design Example

Page 13

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

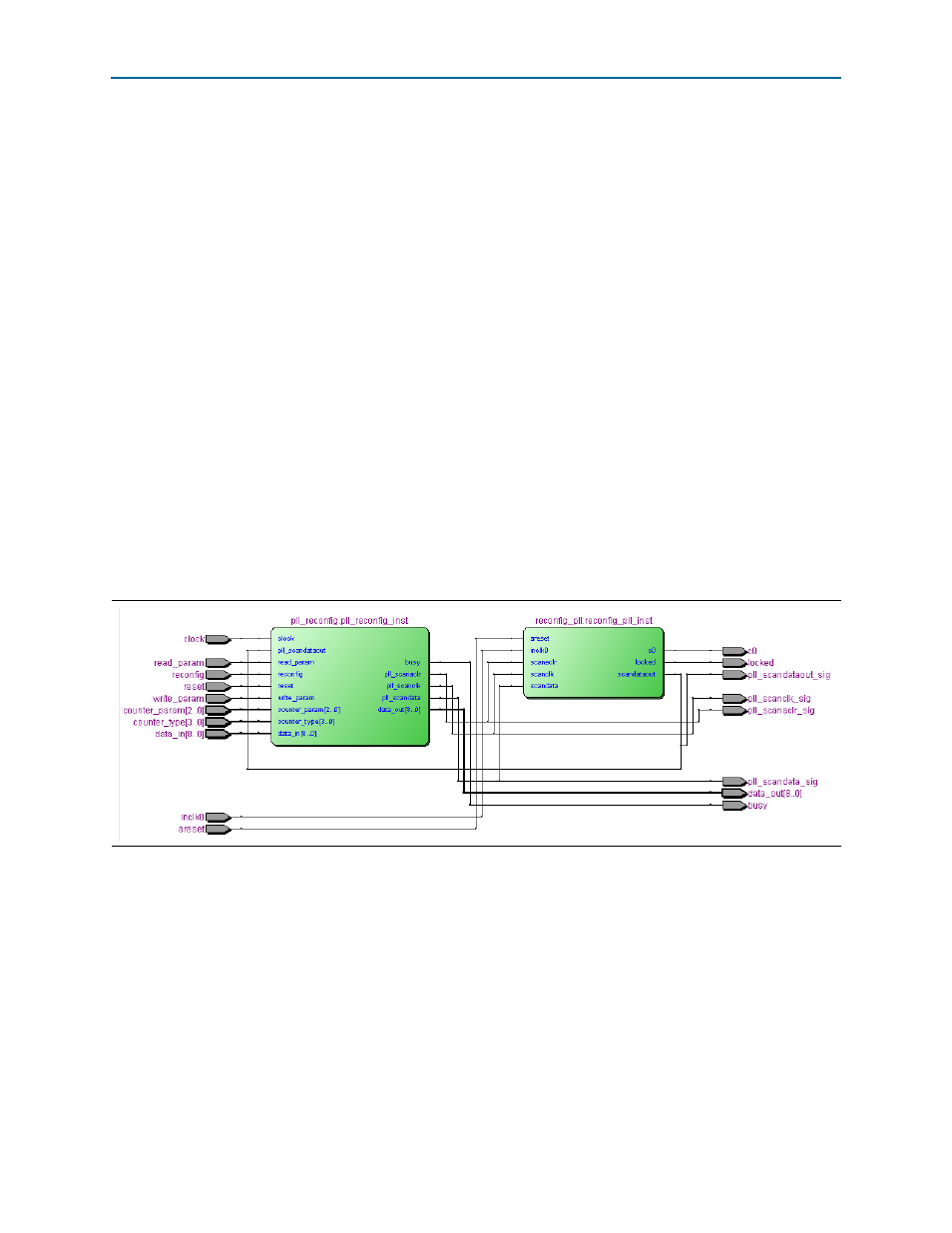

Compiling the ALTPLL and ALTPLL_RECONFIG Megafunctions

To add the ALTPLL megafunction to the ALTPLL_RECONFIG megafunction, and

then compile the design in the Quartus II software, follow these steps:

1. On the Project menu, click Add/Remove File in Project. The Settings dialog box

appears.

2. In the Category

list, select Files.

3. Click Browse (...) after File name and select pll_recon_ex1.vhd from the project

folder. This file is the top-level module that contains the port-mapping between

the

pll_reconfig

and

reconfig_pll

instances.

4. Click Add to add the top-level file to the project.

5. Click OK.

6. On the File menu, click Save Project.

The top-level file is added to the project.

7. To compile the design, on the Processing menu, click Start Compilation.

8. When the Full Compilation was successful message box appears, click OK.

You have now created and compiled the complete design file, which can be viewed in

the RTL Viewer (

). To display the RTL Viewer, in the Tools menu, select

Netlist Viewers

, and click on RTL Viewer.

Simulating the Design Example

To simulate the design example using the ModelSim-Altera software, follow these

steps:

1. Unzip the altpll_reconfig_ex1_msim.zip file to any working directory on your

PC.

2. Browse to the folder in which you unzipped the files.

3. Open remote_update_ex2.do in a text editor.

4. In line 1 of the altpll_reconfig_ex1_msim.do file, ensure that the directory path of

the library files is correct. For example, C:/Modeltech_ae/altera/verilog/stratix.

5. On the File menu, click Save.

Figure 9. RTL Viewer — Complete Design File