Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 9

Functional Description—Implementing Multiple Reconfiguration Using an External ROM

Page 9

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

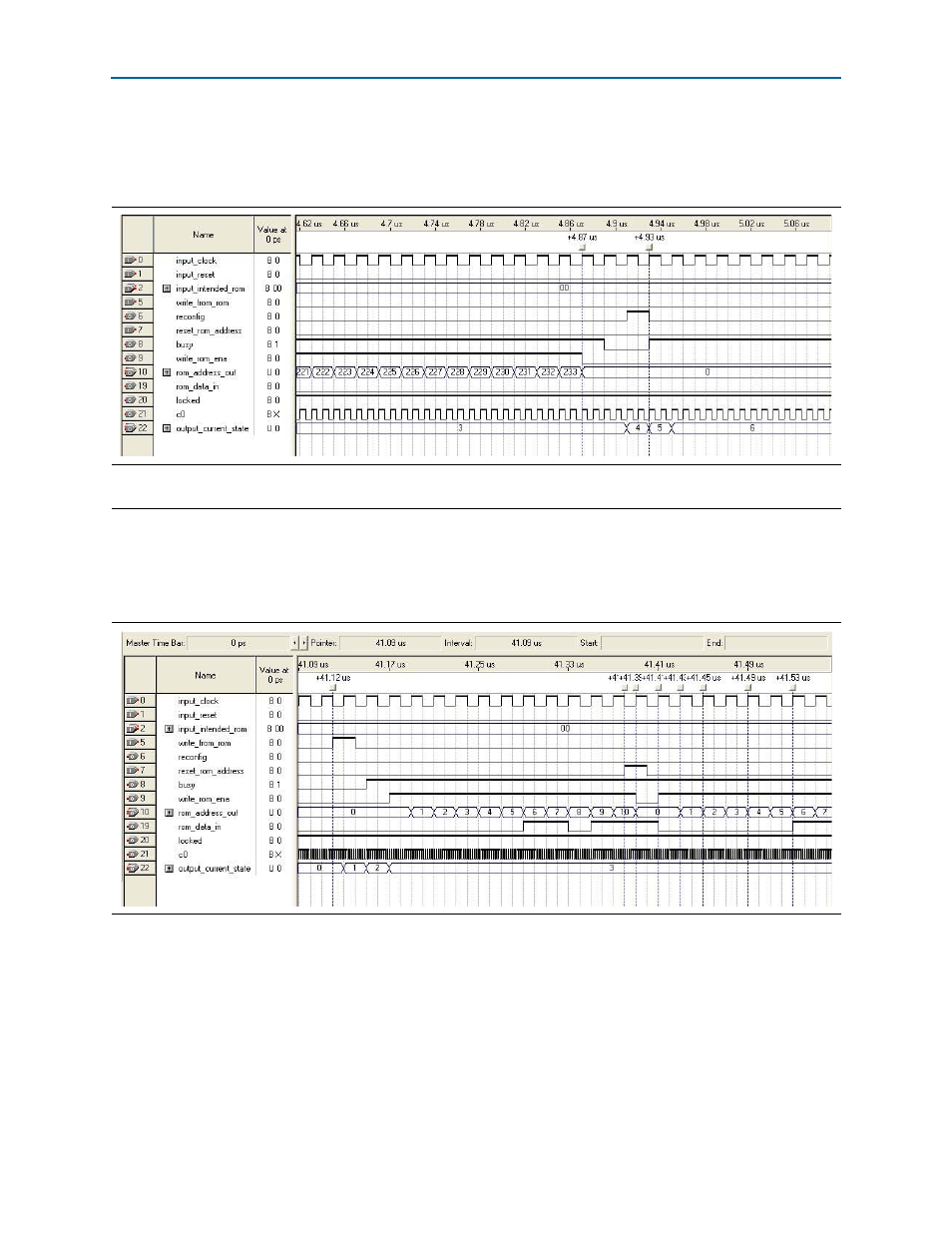

After this, the

reconfig

signal can be asserted for 1 clock cycle to reconfigure the PLL

to the intended settings that have been written to the scan cache of the

ALTPLL_RECONFIG megafunction (refer to

If you assert the

reset

_

rom

_

address

signal, the

write

_

rom

_

ena

signal is deasserted for

1 clock cycle and the

rom_address_out

signal resets. When the

write

_

rom

_

ena

gets

asserted, the write process then restarts from address

0

(refer to

).

Figure 6. Completing Write to the Scan Cache of the ALTPLL_RECONFIG Megafunction from the ROM

Note to

(1) This figure also shows the beginning of the reconfiguration process.

Figure 7. Asserting the reset_rom_address Signal