Sundance SMT329 User Manual

Page 19

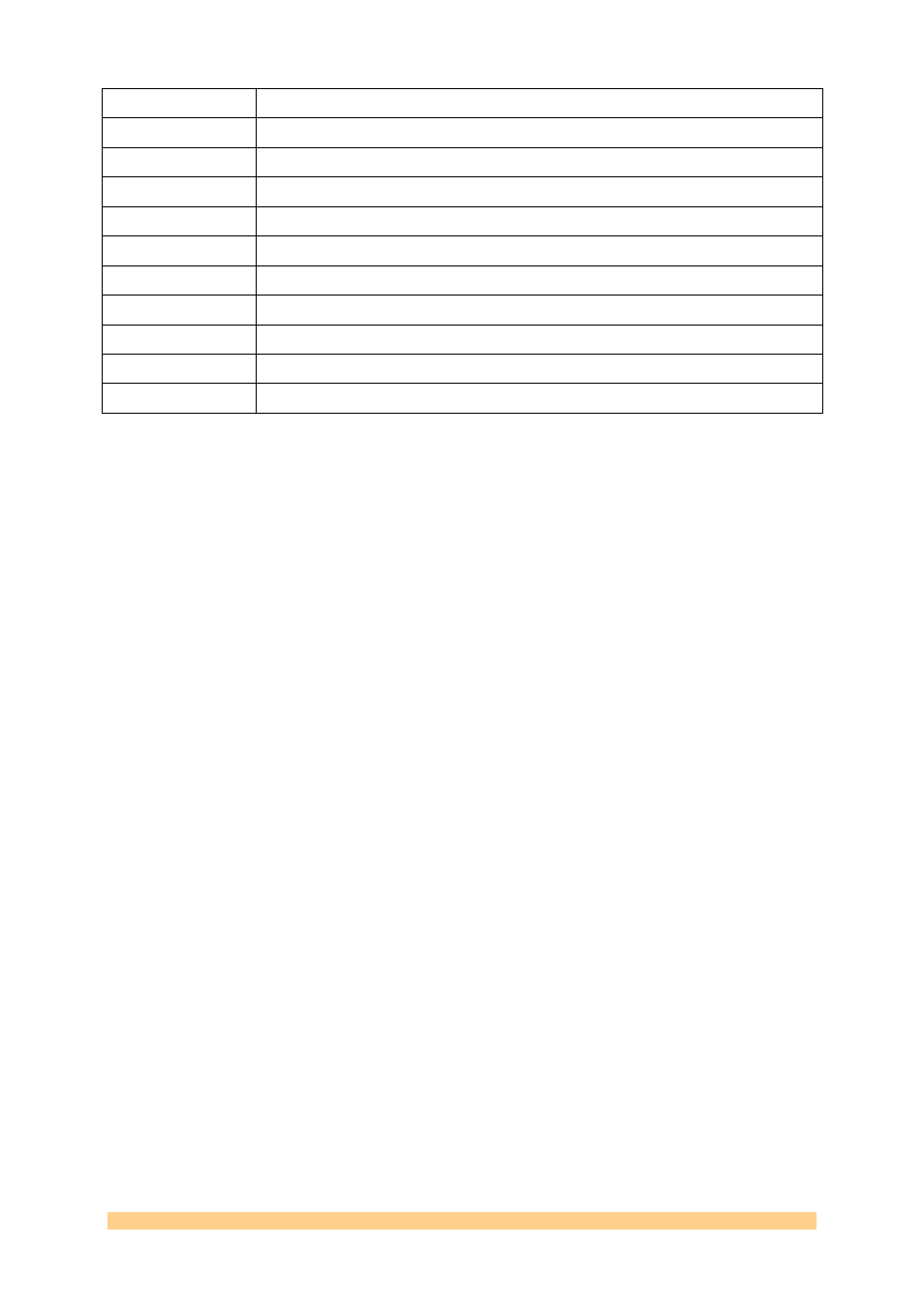

1A

RTO A is connected to this RTI + 0x80 if transmitting

1B

RTO B is connected to this RTI + 0x80 if transmitting

1C

RTO C (VXC1) is connected to this RTI + 0x80 if transmitting

1D

RTO D (VXC2) is connected to this RTI + 0x80 if transmitting

1E 0X1E

1F 0X1F

20

Error map 0

21

Error map 1

22

Spartan3 FPGA revision MSB

23

Spartan3 FPGA revision LSB

24 to FF

<returns the register address>

The error maps are bit maps which have an error bit for each map entry:

Error map 0 has error bits for map entry 7 to 0

Error map 1 has bits 7-4 set to 0, then error bits for map entry 0xB to 8.

Both error maps must be 0 for the switch to be enabled.

The register address is set and the register value read from a single byte address.

Both the VME bus controller and either TIM1 or TIM4 can access it at these addresses:

VME I/O space address offset

=

0xDF

TIM I/O space address

=

0xC0000102

User Manual SMT329

Page 19 of 52 Last

Edited:

09/02/2007

10:58:00