6 tim global bus interface to the sram, Tim global bus interface to the sram – Sundance SMT329 User Manual

Page 30

VME

address

bit

Global

address

bit

Control 4

register

bit

Description

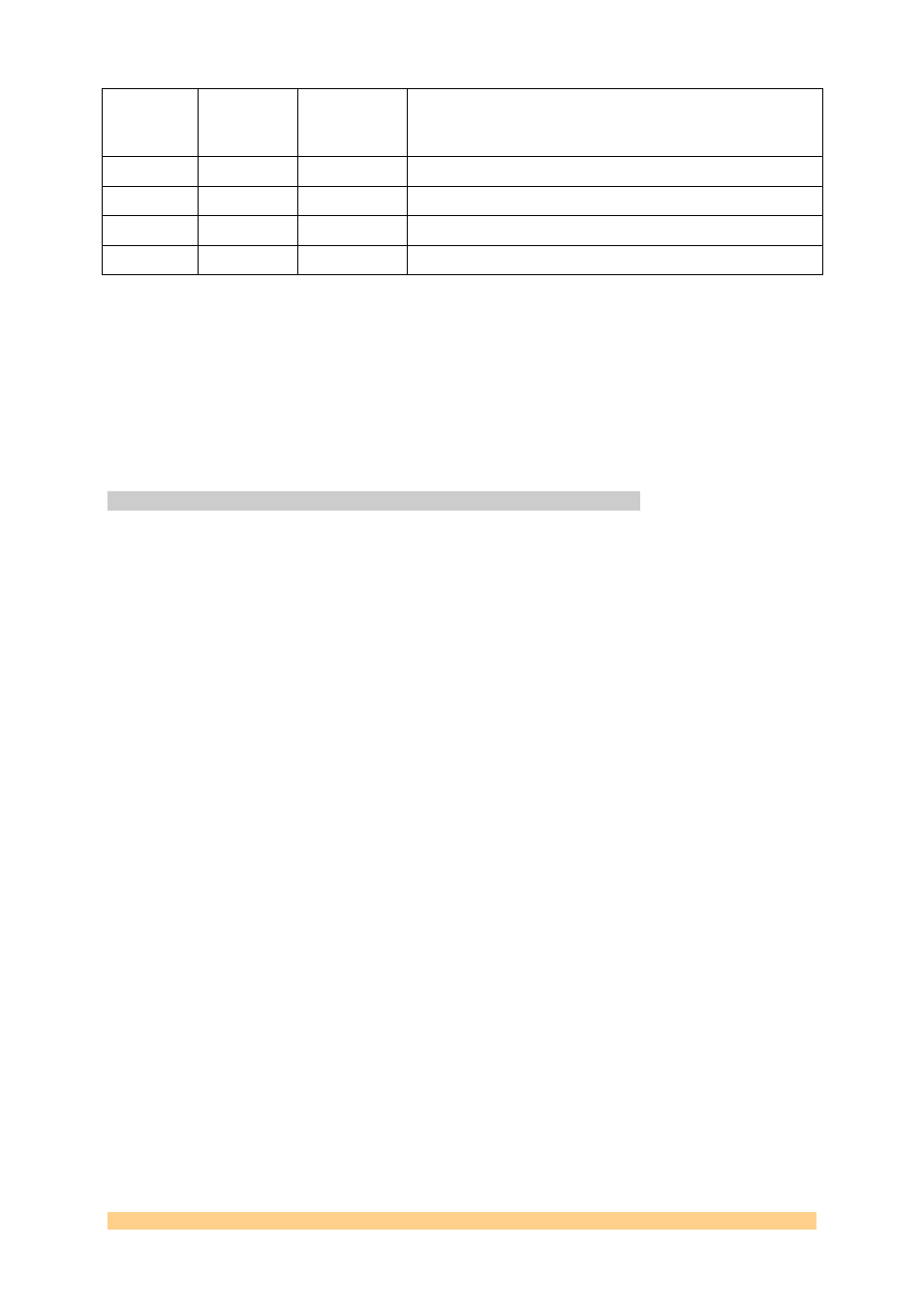

31-24 -

31-24 High

8

bits

23-2

21-0

-

Middle 22 bits

1 - 16 A1

0

-

17

A0 / -Lword

The VME address modifiers, DS0 and DS1 are copied directly from control register 4. The

VME bus request level is also specified in control register4.

So a TIM can directly address 16M bytes in the VME bus address space.

Note that the TIM global bus does not support byte addressing, so transfers to and from the

VME bus are always 32 bits wide.

4.4.6 TIM Global bus interface to the SRAM

This address space occupies global bus addresses in the following region:

0xDFE0 0000 to 0xDFFF FFFF.

This space occupies 2M 32 bit words or 8M bytes.

Note that the TIM global bus does not support byte addressing, so transfers to and from the

sram are always 32 bits wide.

User Manual SMT329

Page 30 of 52 Last

Edited:

09/02/2007

10:58:00