Block diagram – Ensemble Designs BrightEye 57 3G/HD/SD/Analog Test Signal and Sync Pulse Generator User Manual

Page 8

www.ensembledesigns.com

BrightEye 57

TM

BrightEye 57

3G/HD/SD/Analog Test Signal and Sync Pulse Generator User Guide

Page 8

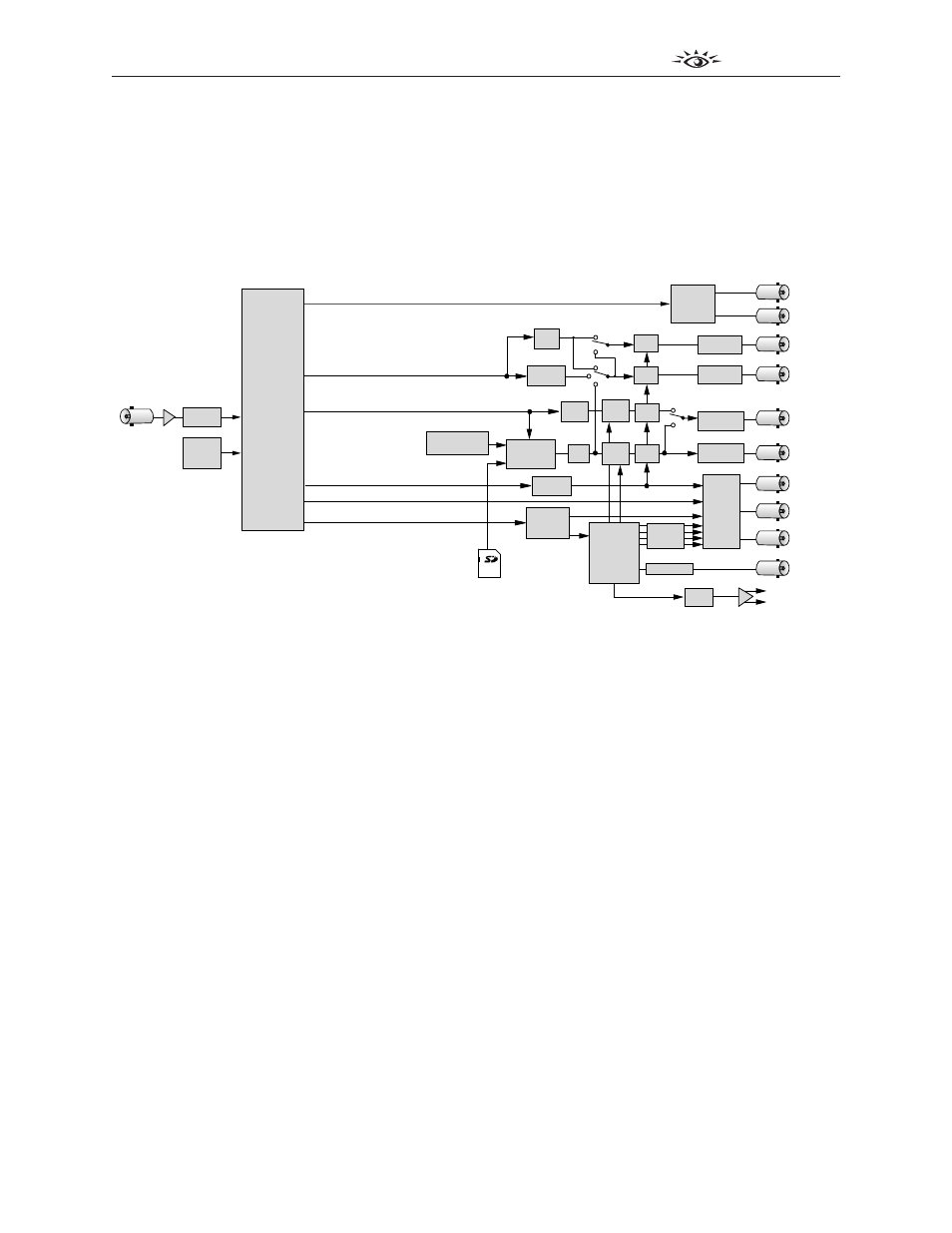

BrightEye 57 Functional Block Diagram, Portrait View

Wordclock

AES 1/2

Aux 1

TLS Out

SDI Out 1

Stereo

DAC

AES Encode

Audio

Generators

Tones and

Silence

Analog Audio

Outputs

SDI Out 2

TLS Out

Composite 1

Composite 2

Tri-Level

Sync

Generator

User Test Patterns Loaded through

built-in Secure Digital Card Interface

Slate

Gen

Standard Internal

Test Patterns

Composite

Encoder

Composite

Encoder

3G/HD/SD

Serializer

3G/HD/SD

Serializer

Audio

Embed

DVITC

Insert

DVITC

Insert

VITC

Insert

VITC

Insert

Audio

Clock

Generator

Aux

Output

Select

Timecode

Generator

Test Signal

Generator

Aux 2

Aux 3

AES

Encoders

6 Hz Pulse

LTC

Black

Gen

Black

Gen

Simple

Colorbars

SDI Output Timing

Composite

Output Timing

TLS Timing

Sync

Reference

Selection

Video/Audio

Clock

Generation

Timing

Adjustments

Audio

Embed

Genlock Input will accept:

525 or 625 Composite

TLS

10 MHz 1VP-P Sine or Square

Internal

Precision

Standard

Sync

Separator

External

Reference

Input

Block Diagram

Please see the functional block diagram on this page and the next page. The block diagram appears

twice, first in a portrait view, then larger in a landscape view.