Core interface path timing analysis, Single data rate input register – Altera GPIO User Manual

Page 17

Related Information

•

Describes techniques for constraining and analyzing source-synchronous interfaces.

Core Interface Path Timing Analysis

To properly perform timing analysis for the core interface paths, you must define the clock settings in

the .sdc for the following:

• clock to the core registers and

• clock to the I/O registers (Simple register and DDIO mode)

To properly perform timing analysis for the I/O interface, specify the system level constraints of the data

pins against the system clock pin in the .sdc.

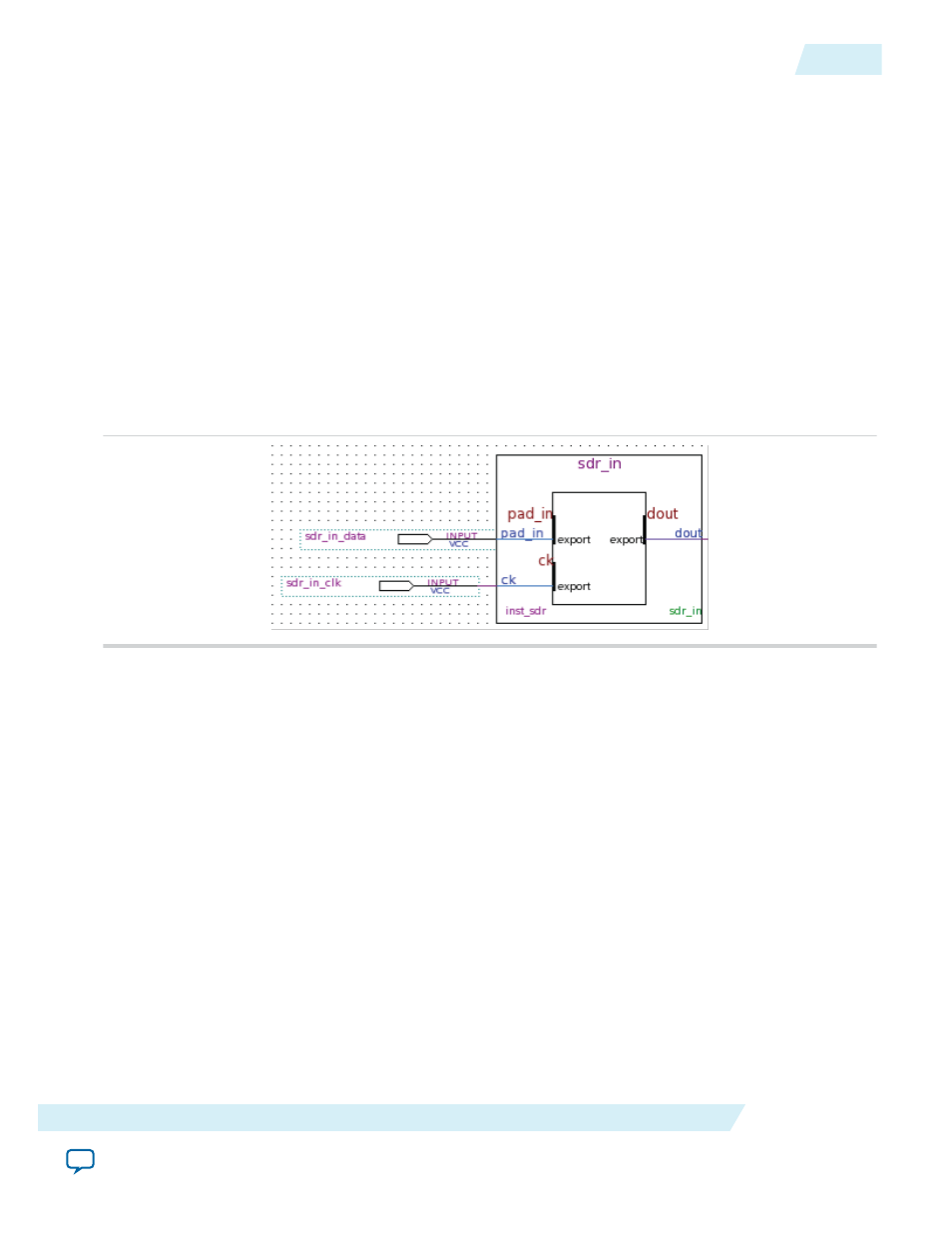

Single Data Rate Input Register

Figure 11: Single Data Rate Input Register

This SDC command creates the clock setting for the input clock:

create_clock -name sdr_in_clk -period "100 MHz" sdr_in_clk

This command instructs the TimeQuest timing analyzer to timing analyze the input I/O with 0.15 ns

input delay.

set_input_delay -clock sdr_in_clk 0.15 sdr_in_data

ug-altera_gpio

2014.08.18

Core Interface Path Timing Analysis

17

Altera GPIO IP Core User Guide

Altera Corporation