Altera gpio delay elements, Timing closure guideline – Altera GPIO User Manual

Page 20

set_output_delay

These commands instruct the TimeQuest Timing Analyzer to timing analyze the positive data and the

negative data against the output clock

set_output_delay -clock ddio_out_fr_outclk 0.55 ddio_out_fr_data

set_output_delay -add_delay -clock_fall -clock ddio_out_fr_outclk 0.55

ddio_out_fr_data

set_false_path

You need these set_false_path commands to stop the TimeQuest timing anaylzer from timing analyzing

the rising edge of the source clock against the falling edge of the output clock and the falling edge of

source clock against rising edge of output clock:

set_false_path -rise_from ddio_out_fr_clk -fall_to ddio_out_fr_outclk

set_false_path -fall_from ddio_out_fr_clk -rise_to ddio_out_fr_outclk

Altera GPIO Delay Elements

The Quartus II software version 14.0a10 does not support automatic setting of delay elements to

maximize slack of I/O timing analysis. You must manually set the delay elements through QSF settings to

close timing or maximize slack on the I/O timing analysis.

You can access the delay elements using these QSF assignments:

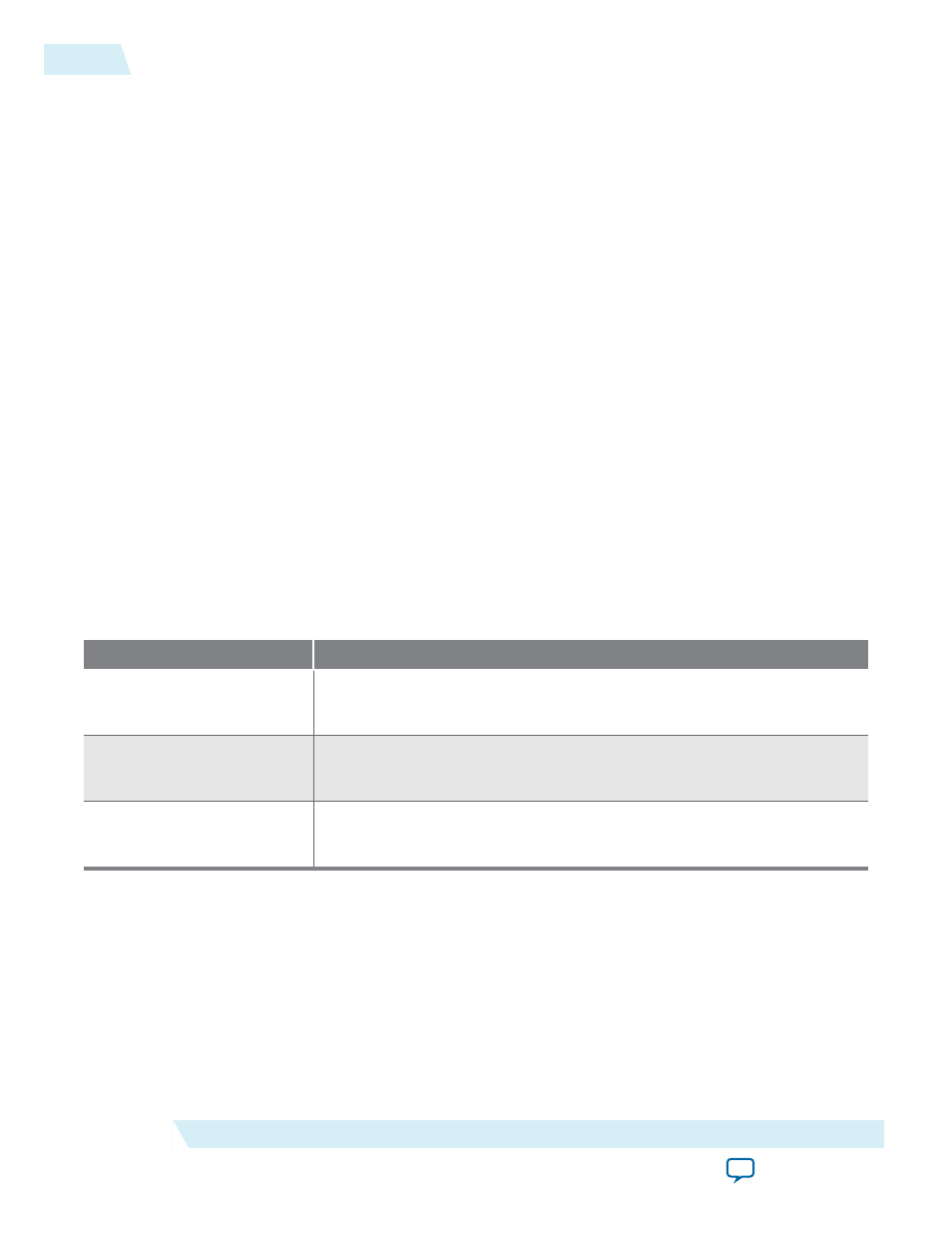

Table 5: QSF Assignments for Altera GPIO Delay Elements

Delay Element

QSF Assignments

Input Delay Element

set_intance_assignment –to <PIN> -name INPUT_DELAY_CHAIN

<0..63>

Output Delay Element

set_intance_assignment –to <PIN> -name OUTPUT_DELAY_CHAIN

<0..15>

Output Enable Delay

Element

set_intance_assignment –to <PIN> -name OE_DELAY_CHAIN

<0..15>

Timing Closure Guideline

For the input registers of the Altera GPIO IP core, if you do not set the input delay chain, it is likely the

input I/O transfer will fail hold time, because the clock delay is larger than the data delay. In such cases,

use the input delay chain to add delay to the input data path to meet hold time. As a general guide, the

input delay chain is about 60 ps per step at -1 speed grade. Dividing the negative hold slack by 60 ps

provides an approximate input delay chain setting to set to pass timing.

However, if the clocks of the GPIO input registers (simple register mode or DDIO mode) are driven by an

I/O phase locked loop (IOPLL), you can choose to set the compensation mode to source synchronous

20

Altera GPIO Delay Elements

ug-altera_gpio

2014.08.18

Altera Corporation

Altera GPIO IP Core User Guide