Altera LVDS SERDES User Manual

Page 10

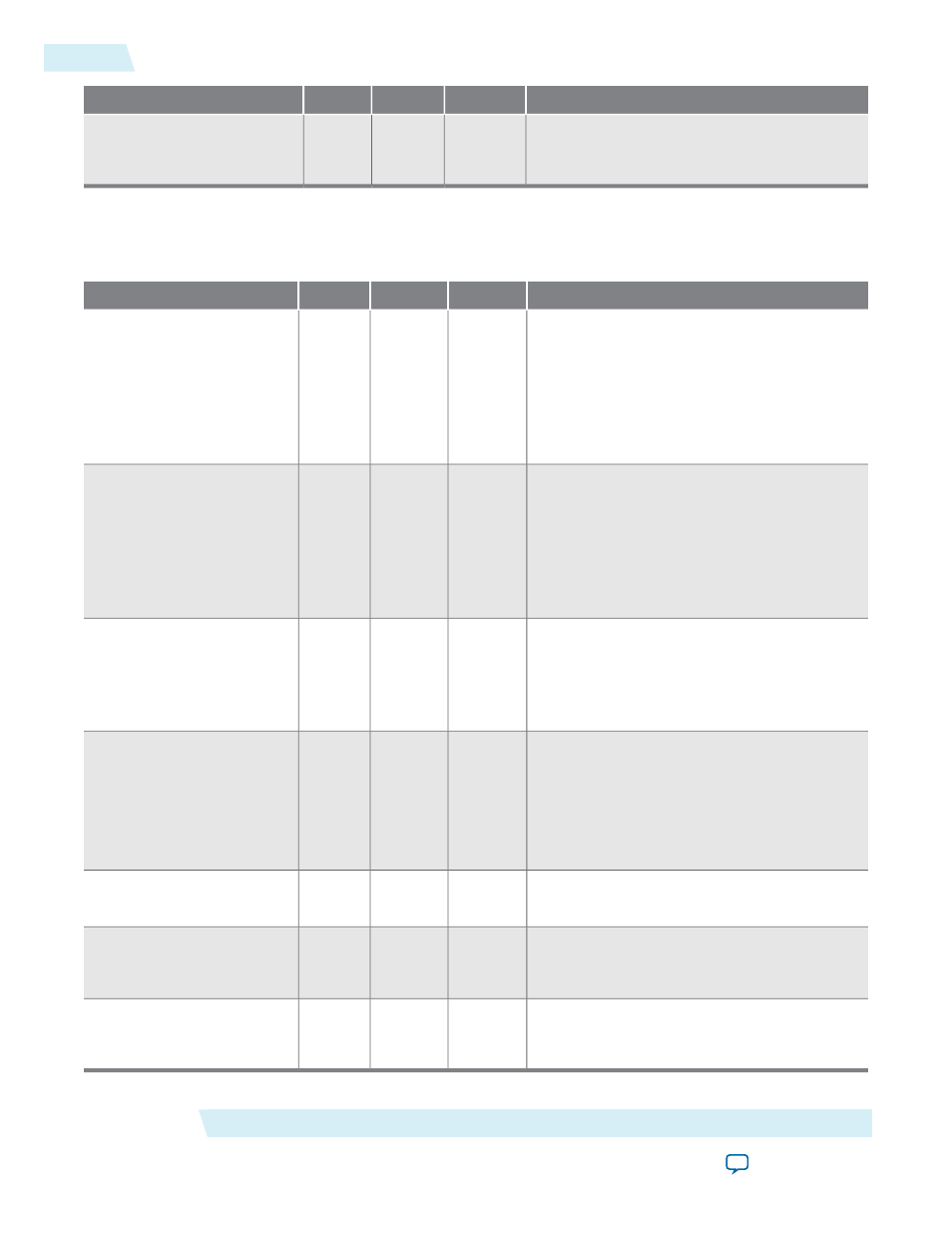

Description

Type

Direction

Width

Signal Name

The clock that drives the core logic feeding the

serializer. Not available in the external PLL

mode.

Clock

Output

1

tx_coreclock

Table 5: External PLL Signals

For instructions on setting the frequencies, duty cycles, and phase shifts of the required PLL clocks for external PLL

mode, refer to the Clock Resource Summary tab in the IP Parameter Editor.

Description

Type

Direction

Width

Signal Name

LVDS fast clock. Used for serial data transfer.

Required in all modes. You must connect this

signal to the

lvds_clk[0]

port of the PLL.

This signal is configured as

outclock[0]

from

the PLL. Use Enable access to PLL LVDS_

CLK/LOADEN output port in the IOPLL

generation.

Clock

Input

1

ext_fclk

LVDS load enable. Used for parallel load. Not

required in RX Soft-CDR mode. You must

connect this signal to the

loaden[0]

port of

the PLL. This signal is configured as

outclock[1]

from the PLL. Use Enable access

to PLL LVDS_CLK/LOADEN output port

in the IOPLL generation.

Clock

Input

1

ext_loaden

The clock that drives the core logic feeding the

serializer (TX) / receiving from the deserializer

(RX). This signal is still present in RX soft-

CDR mode, even though the RX core registers

are clocked using the

rx_divfwdclk

.

Clock

Input

1

ext_coreclock

Required for RX DPA-FIFO and RX Soft-CDR

modes only. Provides the VCO clocks to the

DPA circuitry for optimal phase selection. You

must connect this signal to the

phout[7:0]

signal from the PLL. Use Enable access to PLL

DPA output port in IOPLL generation.

Clock

Input

ext_vcoph[7:0]

PLL lock signal. Required for RX DPA-FIFO

and RX Soft-CDR modes only.

Data

Input

1

ext_pll_locked

Phase-shifted version of fast clock required

for TX outclock phase shifts that are not

multiples of 180 degrees.

Clock

Input

1

ext_tx_outclock_fclk

Phase-shifted version of loaden required for

TX outclock phase shifts that are not multiples

of 180 degrees.

Clock

Input

1

ext_tx_outclock_loaden

Altera LVDS SERDES IP Core User Guide

Altera Corporation

ug_altera_lvds

Signals

10

2014.08.18