Altera User Flash Memory User Manual

Page 11

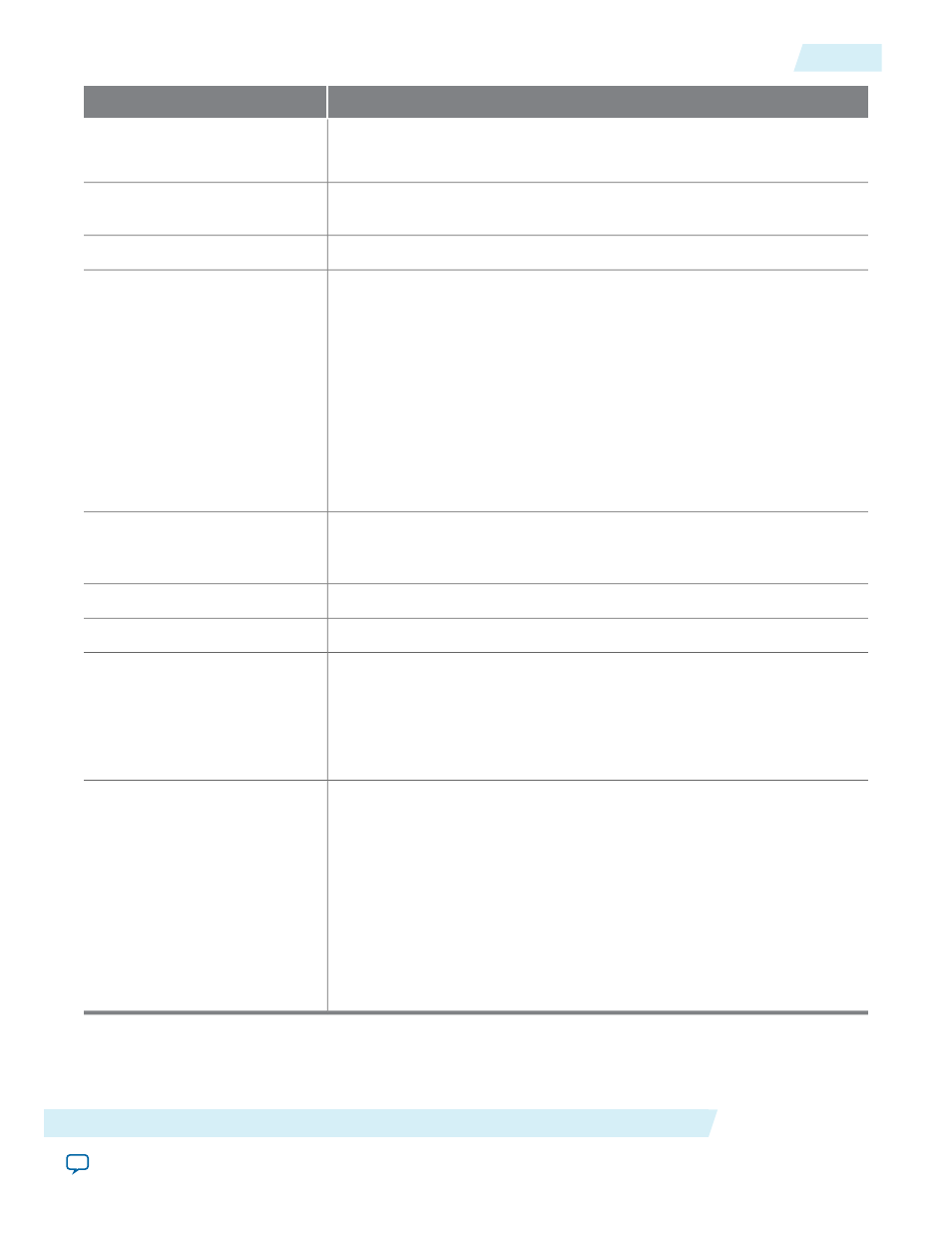

Description

Configuration Setting

Select Base mode to use 8-bit address and data.

Select Extended mode to use16-bit address and data.

Configuration mode

Turn on this option to route the oscillator frequency to an external oscillator

port.

Use ‘osc’ output port

Turn on this option to enable the oscillator enable port.

Use ‘oscena’ input port

• Select Initialize blank memory if you do not want to specify any initial-

ization file. Select Initialize from hex or mif file to specify the initialization

file. Type the file name or browse for the required file.

• In the Quartus II software, the memory content values from your .hex

or .mif are hard-coded into your ALTUFM IP core variation file when

you generate the IP variation. If you change the contents of your .hex or

.mif after generating the IP variation, these updates will not be reflected

in simulation. This may cause a mismatch between simulation and device

behavior because compilation and program file generation in the Quartus

II software use the current .hex or .mif contents instead of the hard-coded

values.To avoid this mismatch, regnenerate the ALTUFM IP core

whenever you update your .hex or .mif.

Memory content initialization

Specify the oscillator frequency for the user flash memory. This parameter

is used for simulation purposes only. The values are 5.56MHz and 3.33MHz.

If omitted, the default is 5.56MHz.

Oscillator frequency

Specify the erase time.

Erase time

Specify the program time.

Program time

Turn on this option if you want to generate a netlist for your third-party

EDA synthesis tool to estimate the timing and resource usage of the IP core.

If you turn on this option, a netlist file (_syn.v) is generated. This file is a

representation of the customized logic used in the Quartus II software and

provides the connectivity of the architectural elements in the IP core but

may not represent true functionality.

Generate netlist

Specify the types of files to be generated. The Variation file (<function name>

.v) contains wrapper code in the language you specified on page 2a and is

automatically generated. Choose from the following types of files:

• AHDL Include file (<function name>. inc)

• VHDL component declaration file (<function name>.cmp)

• Quartus II symbol file (<function name>.bsf)

• Instantiation template file (<function name>_inst.v)

• Verilog HDL black box file (<function name>_bb.v)

For more information about the wizard-generated files, refer to the

Introduction to Altera IP Cores.

Summary Page

Altera Corporation

Altera User Flash Memory (ALTUFM) IP Core User Guide

11

Parameter Settings

UG-040105

2014.08.18