Altera Nios II Embedded Evaluation Kit Cyclone III Edition User Manual

Page 26

Advertising

Altera Corporation

Development Board Version 1.0.

3–2

July 2010

Nios II Embedded Evaluation Kit, Cyclone III Edition

Nios II Processor Systems

Touch panel. The video pipeline signals have been multiplexed inside the

FPGA and de-multiplexed by the MAX II CPLD to provide a full range of

functionality on the daughter card over a limited number of pins on the

HSMC connector. (see the LCD Multimedia Daughtercard Reference Manual

for details)

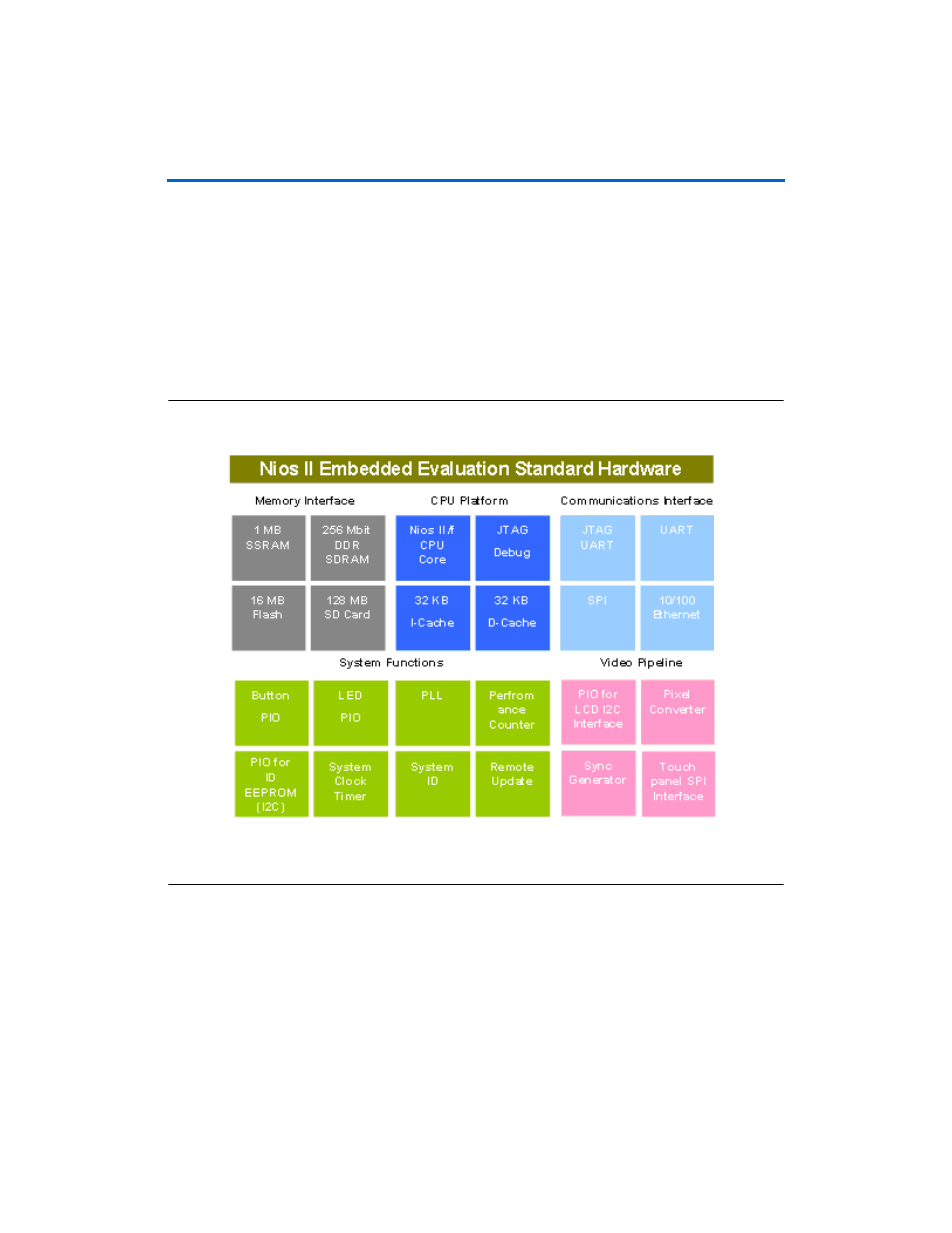

Within the FPGA is the Nios II Video Processor System. It is a pre-

generated Nios II processor based hardware system that can be used as a

starting point for embedded application development. The components

in this embedded microprocessor system are shown in

.

Figure 3–2. Nios II Processor System Block Diagram

Advertising