Altera Nios II Embedded Evaluation Kit Cyclone III Edition User Manual

Page 48

Altera Corporation

5–12

July 2010

Nios II Embedded Evaluation Kit, Cyclone III Edition

Design Examples

The implementation is fixed point with all values pre-scaled by

0x10000000. The loop will continue until the number of iterations reaches

‘max_iter’ or x

2

+ y

2

converges to the value of 4. This function is called for

each pixel so for this design that would be 384000 times since the screen

resolution is 800x480. The value of ‘iter’ is used as the index into the color

palette which picks the color of the pixel displayed on the screen. Even

though the main processor supports dynamic branch prediction and

contains cache memory, this operation of filling the screen can be very

time consuming.

The approach taken for the C2H accelerated version is to offload this

algorithm to pipelined and parallel hardware. Each Mandelbrot engine

contains dedicated multiply, addition, and subtraction logic to perform

multiple operations in parallel. Each Mandelbrot accelerator operates on

a quarter of the frame and is only called once per frame. The workload is

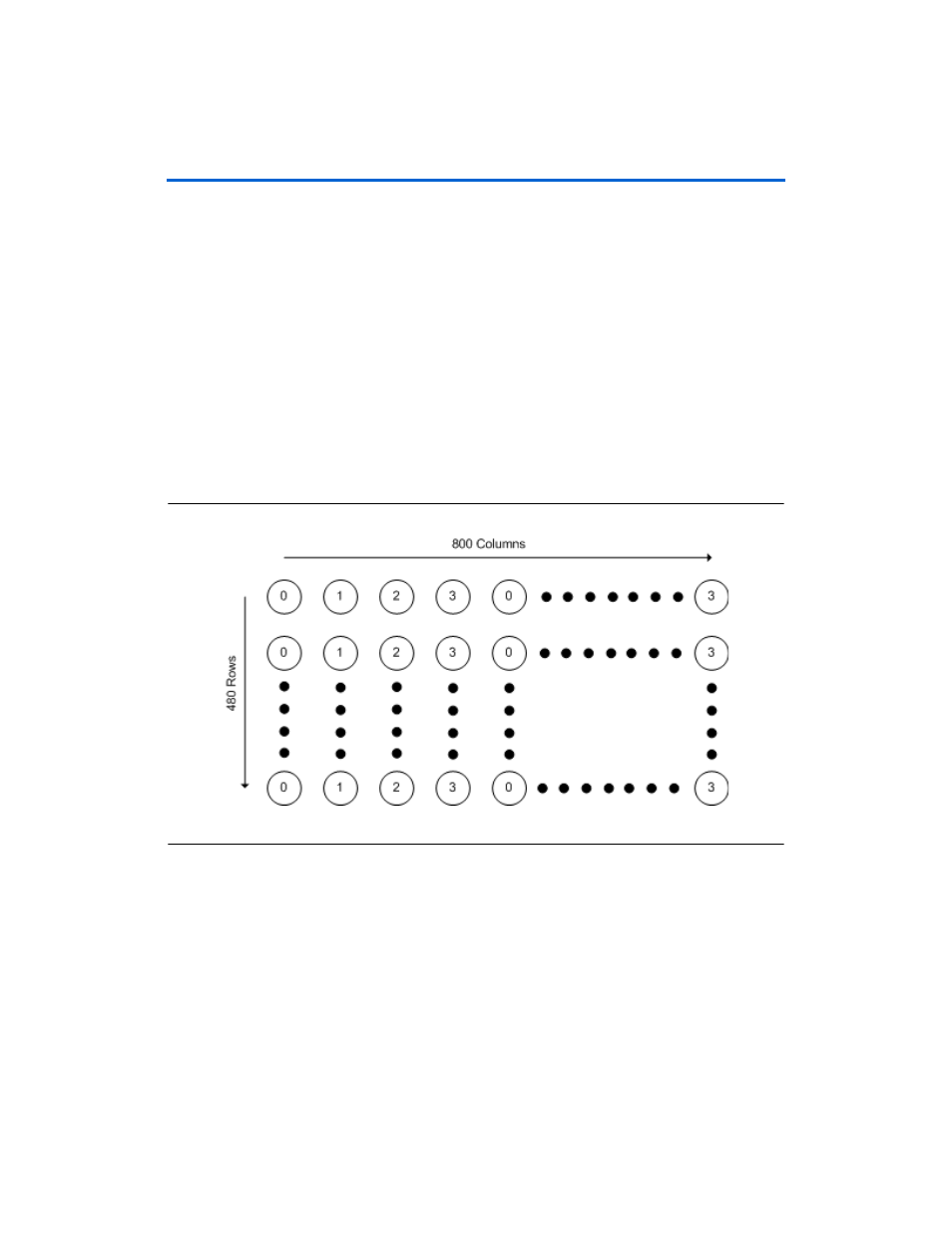

distributed on a pixel basis so each accelerator handles every fourth pixel.

Figure 5–9. Mandelbrot Engine Pixel Interleaving

While the hardware accelerators are calculating a frame, the coordinates

of the next frame are prepared by the main i.e. the Nios II processor. The

hardware accelerators contain a C pragma that instructs the compiler to

implement non-blocking accelerators which allows both the main

processor and Mandelbrot hardware accelerators to operate in parallel.

The main processor polls the hardware accelerator to determine if the

entire frame has been rendered.