Avalon-st source interface – Altera FIR Compiler II MegaCore Function User Manual

Page 39

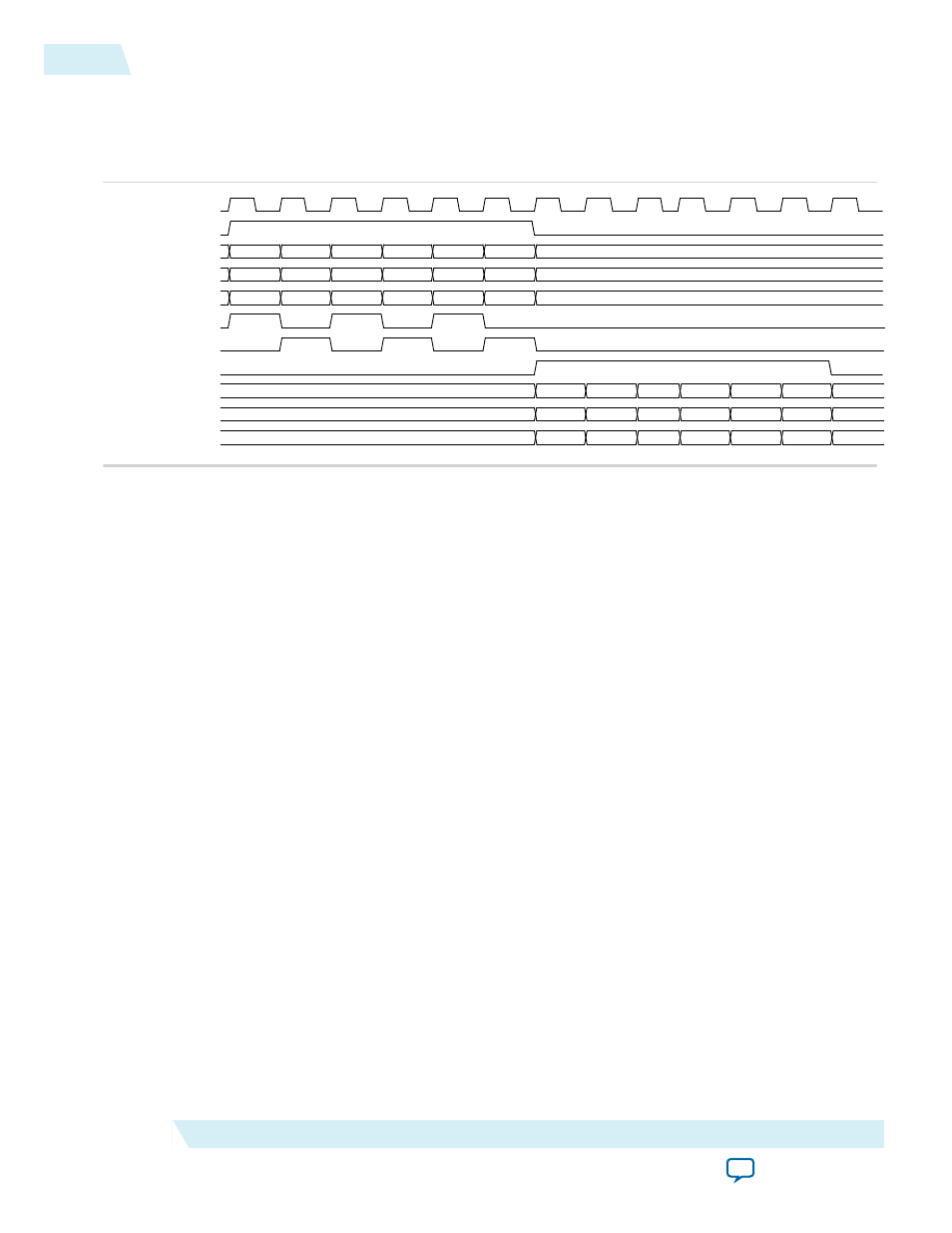

Figure 4-5: Timing Diagram of Multiple Channels on Multiple Wires

The sink interface to the FIR II IP core when transferring a packet of data over multiple channels on

multiple wires. The data width of each channel is 8 bits. Number of channels = 6, clock rate = 200 MHz,

and sample rate = 100 MHz

clk

ast_sink_valid

ast_sink_data[7:0]

ast_sink_data[15:8]

ast_sink_data[23:16]

ast_sink_sop

ast_sink_eop

xln_v[7:0]

xln_0[7:0]

xln_1[7:0]

xln_2[7:0]

A0

B0

A1

B1

A2

B2

C0

D0

C1

D1

C2

D2

E0

F0

E1

F1

E2

F2

A0

B0

A1

B1

A2

B2

C0

D0

C1

D1

C2

D2

E0

F0

E1

F1

E2

F2

X

X

X

Avalon-ST Source Interface

The source interface can handle single or multiple channels on a single wire and multiple channels on

multiple wires. The IP core includes an Avalon-ST FIFO in the source wrapper when the backpressure

support is turned on. The Avalon-ST FIFO controls the backpressure mechanism and catches the extra

cycles of data from the FIR II IP core after backpressure. On the input side of the FIR II IP core, driving

the

enable_i

signal low, causes the FIR II IP core to stop. From the output side, backpressure drives the

enable_i

signal of the FIR II IP core. If the downstream module can accept data again, the FIR II IP core

is instantly re-enabled.

When the packet size is greater than one (multichannel), the source interface expects your application to

supply the count of data starting from 1 to the packet size. When the source interface receives the

valid

flag together with the

data_count

= 1, it starts sending out data by driving both the

ast_source_sop

and

ast_source_valid

signals high. When

data_count

equals the packet size, the

ast_source_eop

signal is

driven high together with the

ast_source_valid

signal.

If the downstream components are not ready to accept any data, the source interface drives the

source_stall

signal high to tell the design to stall.

4-6

Avalon-ST Source Interface

UG-01072

2014.12.15

Altera Corporation

FIR II IP Core Functional Description