Altera FIR Compiler II MegaCore Function User Manual

Page 42

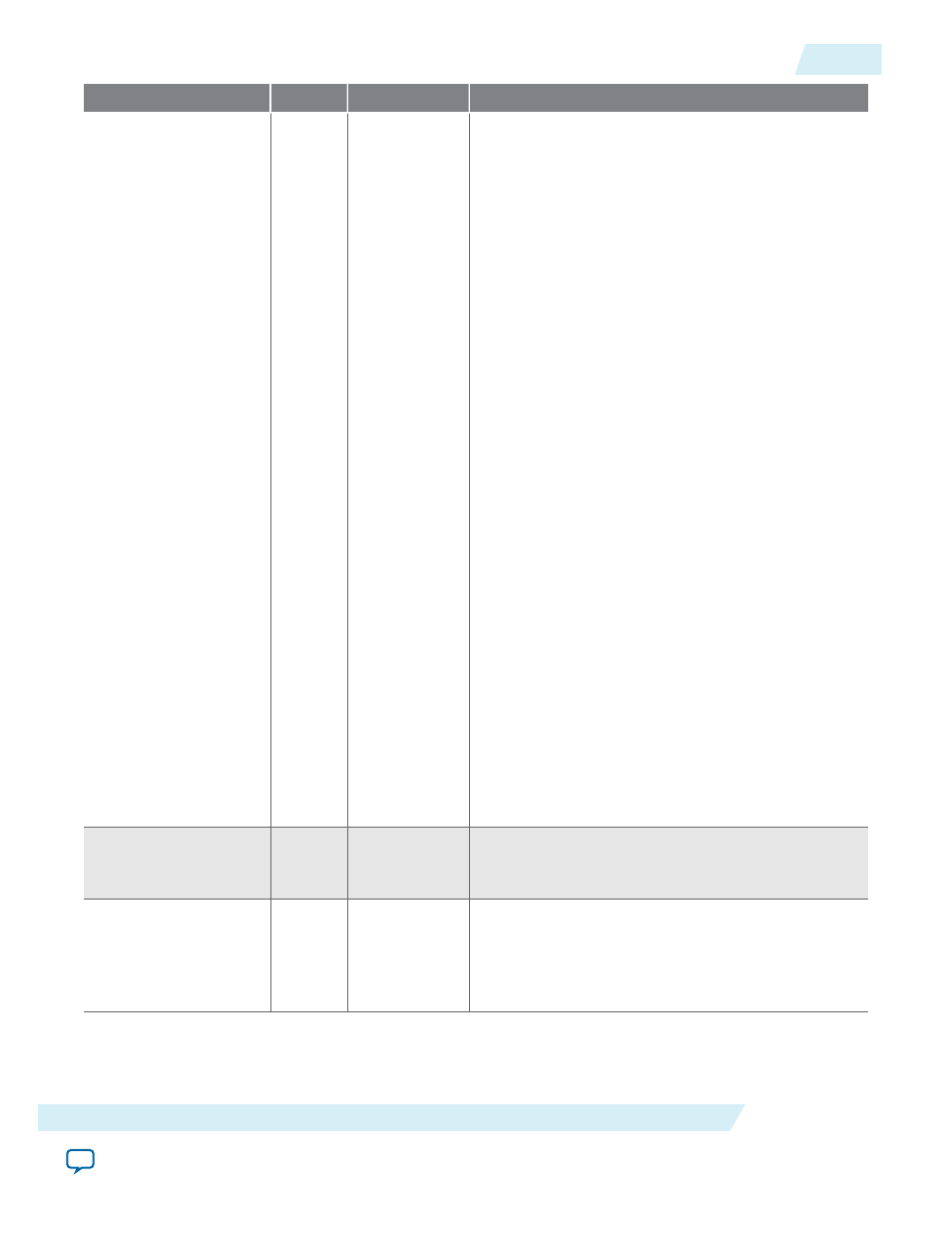

Signal

Direction

Width

Description

ast_sink_data

Input

(Data width +

Bank width) ×

the number of

channel input

wires

(PhysChanIn)

where,

Bank width=

Log2(Number

of coefficient

sets)

Sample input data. For a multichannel operation

(number of channel input wires > 1), the least signifi‐

cant bits of

ast_sink_data

are mapped to

xln_0

of

the FIR II IP core filter.

For example:

ast_sink_data[7:0]

-->

xln_0[7:0]

ast_sink_data[15:8]

-->

xln_1[7:0]

ast_sink_data[23:16]

-->

xln_2[7:0]

For multiple coefficient banks, the most significant

bits of the channel data are mapped to the bank

input signal and the LSBs of the channel data are

mapped to the data input signal.

For example,

Single channel with 4 coefficient banks:

ast_sink_data[9:8] --> BankIn_0

ast_sink_data[7:0] --> xln_0

Multi-channel (4 channels) with 4 coefficient banks:

ast_sink_data[9:8] --> BankIn_0

ast_sink_data[7:0] --> xln_0

ast_sink_data[19:18] --> BankIn_1

ast_sink_data[17:10] --> xln_1

ast_sink_data[29:28] --> BankIn_2

ast_sink_data[27:20] --> xln_2

ast_sink_data[39:38] --> BankIn_3

ast_sink_data[37:30] --> xln_3

ast_sink_sop

Input

1

Marks the start of the incoming sample group. The

start of packet (SOP) is interpreted as a sample from

channel 0.

ast_sink_eop

Input

1

Marks the end of the incoming sample group. If data

is associated with N channels, the end of packet

(EOP) must be driven high when the sample

belonging to the last channel (that is, channel N-1),

is presented at the data input.

UG-01072

2014.12.15

FIR II IP Core Signals

4-9

FIR II IP Core Functional Description

Altera Corporation