Altera FIR Compiler II MegaCore Function User Manual

Page 56

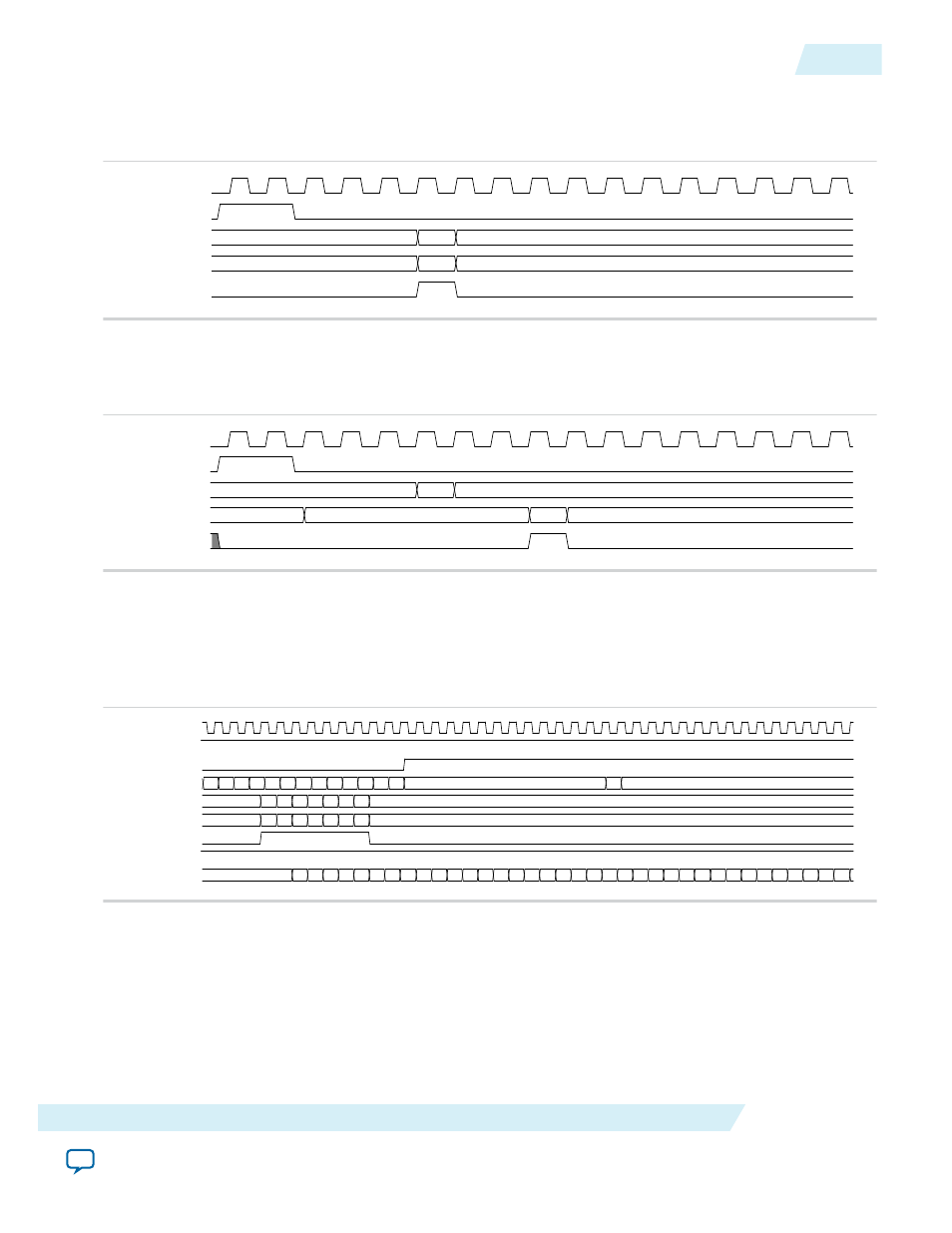

Figure 4-31: Timing Diagram of Coefficient Reloading in Write mode

In this mode, the IP core loads one coefficient data. The new coefficient data (123) loads into a single

address (7)

clk

coeff_in_areset

coeff_in_address[11:0]

coeff_in_data[15:0]

coeff_in_we[0]

-1

7

0

123

-1

0

Figure 4-32: Timing Diagram of Coefficient Reloading in Read mode

When the coeff_in_address is 3, the IP core reads coefficient data at the location, the coefficient data 80 is

available on coeff_out_data when the coeff_out_valid signal is high.

clk

coeff_in_areset

coeff_in_address[11:0]

coeff_out_data[15:0]

coeff_out_valid[0]

-1

3

0

0

80

-1

Figure 4-33: Timing Diagram of Multiple Coefficient Banks

It is a symmetry, 13-tap filter. The IP core reloads coefficients data of bank 1 (address 7-13) while the filter

is running on bank 0. When the coefficient reloading is completed, bank 1 is used to produce an impulse

response of the filter and you can observe the new coefficient data (-58,18,106…) from bank 1 on the filter

output.

clk

xin_v[0]

bankin_0[0]

xin_0[7:0]

coeff_in_data[15:0]

coeff_in_address[11:0]

coeff_in_we[0]

xout_v[0]

xout_0[19:0]

51 -14 -48 33 112 125 -10 -71 119 40 -105 -125-114

0

1

0

-58 18 106 -34 119 112 105 -1

7 8

9 10 11 12 13

342 15303636549064008064 11 16 20 20 23 28 30 26 16 12 -14 12 -22 -51 -27

-26 -13

51986612 0 -58 18 106

119 112 105 112

-1

6

0

-1

-13

-82

-34

UG-01072

2014.12.15

FIR II IP Core Coefficient Reloading

4-23

FIR II IP Core Functional Description

Altera Corporation