Altera FIR Compiler II MegaCore Function User Manual

Page 9

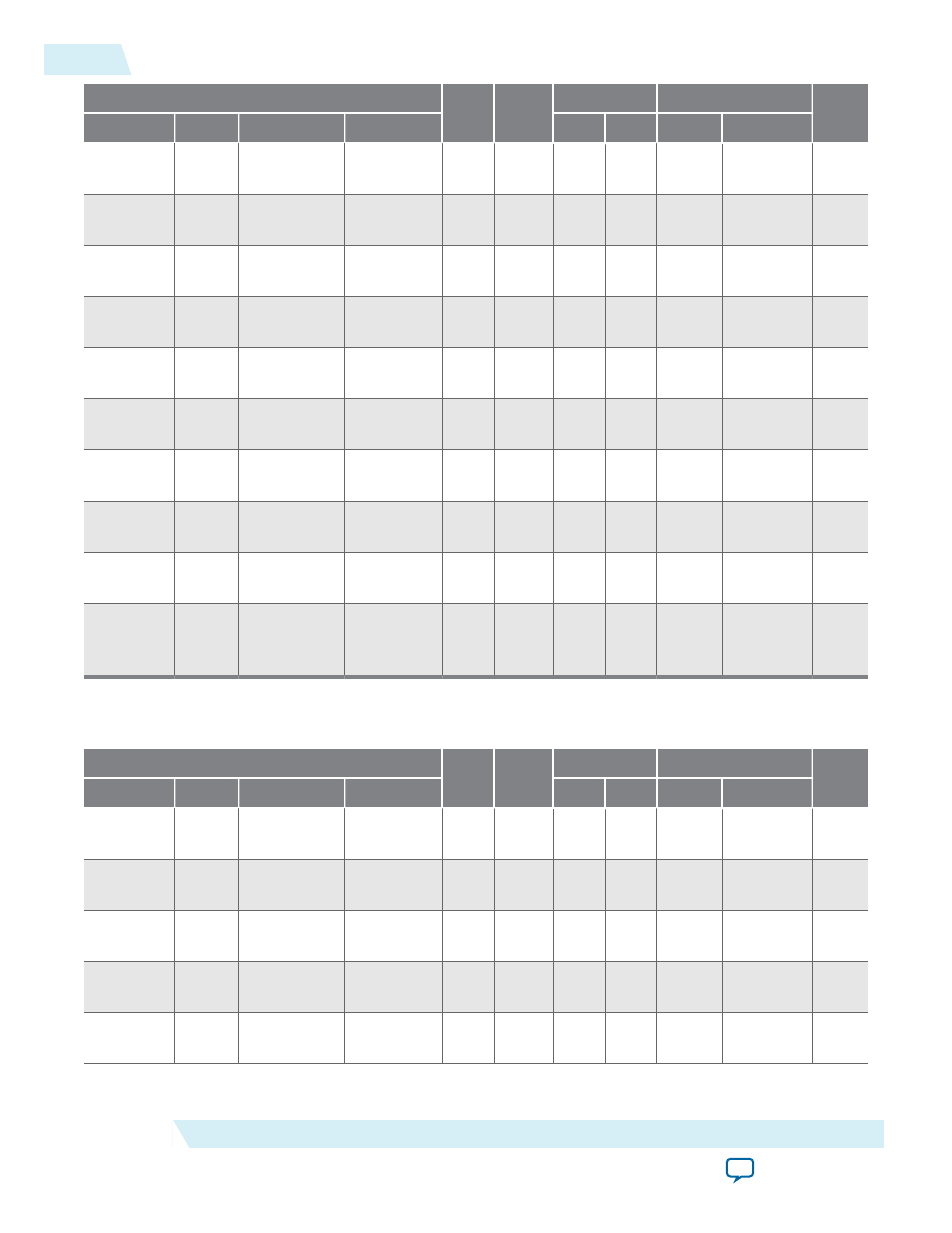

Parameters

ALM

DSP

Blocks

Memory

Registers

f

MAX

(MHz)

Channel

Wires

Filter Type

Coefficients

M10K M20K Primary Secondary

1 Half

Band

—

Interpolation —

254

3

0

—

293

8

31

0

1 Half

Band

—

Interpolation Write

333

4

0

—

314

10

30

9

1

—

Single rate

—

93

10

0

—

129

27

29

9

1 super

sample

—

Single rate

—

262

20

0

—

307

41

30

9

1 super

sample

—

Single rate

Write

373

20

0

—

687

40

30

2

1

—

Single rate

Write

228

10

0

—

519

16

30

0

1 Half

Band

—

Single rate

—

189

5

0

—

254

63

30

9

1 Half

Band

—

Single rate

Write

272

5

0

—

496

29

31

0

1

—

Single rate

Multiple

banks

109

10

0

—

199

29

28

3

1

—

Single rate

Multiple

banks;

Write

395

10

0

—

361

19

28

2

Table 1-4: FIR II IP Core Performance—Cyclone V Devices

Typical expected performance using the Quartus II software with Cyclone V (5CGXFC7D6F31C6) devices.

Parameters

ALM

DSP

Blocks

Memory

Registers

f

MAX

(MHz)

Channel

Wires

Filter Type

Coefficients

M10K M20K Primary Secondary

8

2

Decimation

—

1,607 24

0

—

1,231

46

27

3

8

2

Decimation

Write

2,092 24

0

—

1,352

63

27

3

8

2

Fractional

Rate

—

1,852 16

0

—

3,551

309

25

4

8

2

Fractional

Rate

Write

2,203 16

0

—

3,675

269

25

5

8

2

Fractional

Rate

—

1,951 16

0

—

3,543

421

22

7

1-6

FIR II IP Core Performance and Resource Utilization

UG-01072

2014.12.15

Altera Corporation

About the FIR II IP Core