Ports and parameters, Lpm_shiftreg megafunction input ports – Altera Shift Register IP Core User Manual

Page 12

Ports and Parameters

The options listed in this section describe all of the ports and parameters available for each device to customize

the LPM_SHIFTREG megafunction according to your application.

The parameter details are only relevant for users who bypass the MegaWizard

®

Plug-In Manager interface

and use the megafunction as a directly parameterized instantiation in their design. The details of these

parameters are hidden from the user of the MegaWizard Plug-In Manager interface.

LPM_SHIFTREG Megafunction Input Ports

on page 12

LPM_SHIFTREG Megafunction Output Ports

on page 13

LPM_SHIFTREG Megafunction Parameters

on page 13

LPM_SHIFTREG Megafunction Input Ports

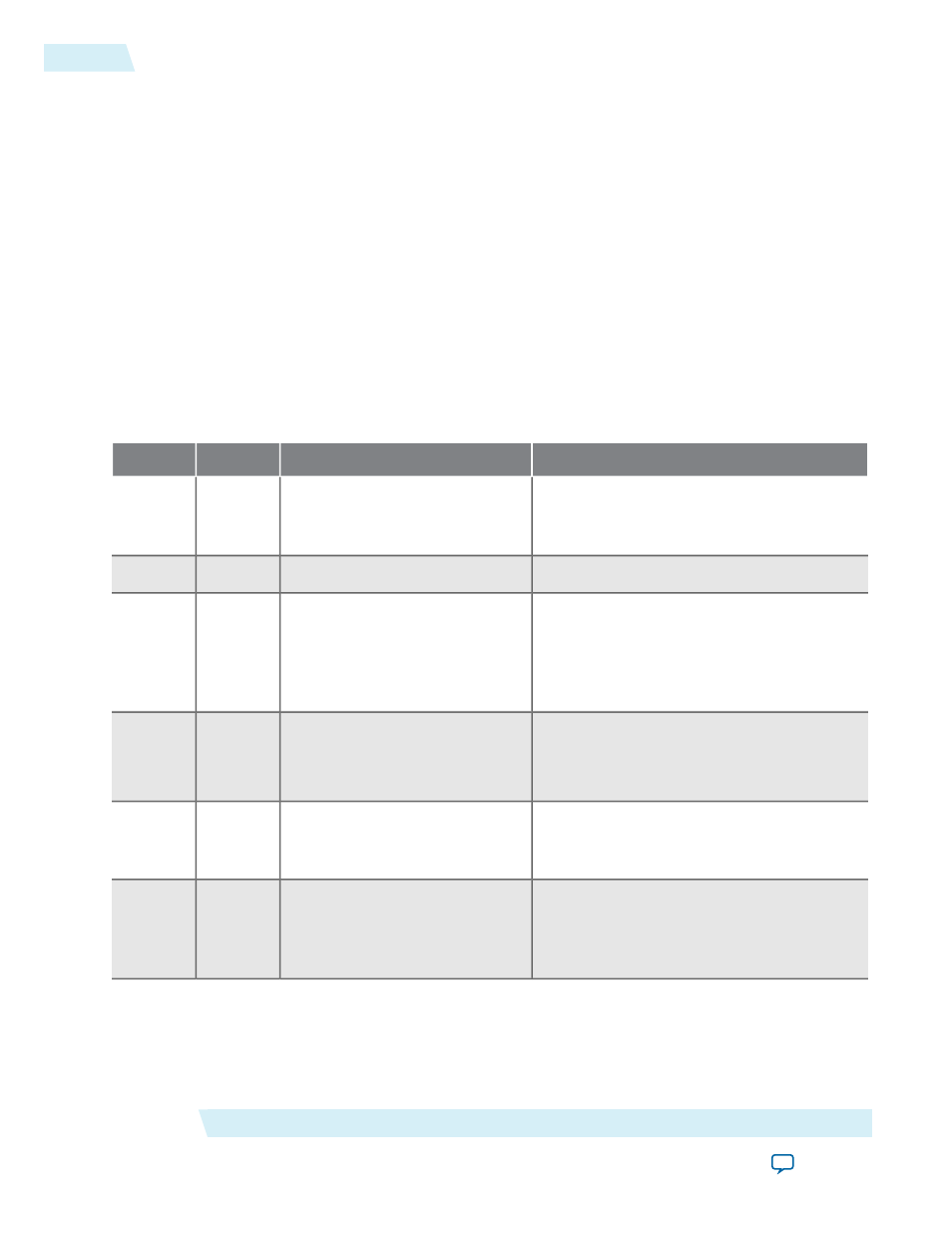

Table 3: Input Ports for the LPM_SHIFTREG Megafunction

Comments

Description

Required

Port Name

Input port LPM_WIDTH wide. At least one of

data

, aset, aclr, sset, sclr and/or

shiftin

ports must be used.

Data input to the shift register.

No

data[]

Positive-edge-triggered clock.

Yes

clock

Shift options use enable input for clock enable.

Enable must be high (1) or unconnected for serial

operation. Load must be high (1) and enable

must be high or unconnected for parallel load

operation.

Clock enable input.

No

enable

At least one of data, aset, aclr, sset, sclr

and/or shiftin ports must be used.

Default value is VCC.

Serial shift data input.

No

shiftin

Default is low (0) shift operation. For parallel

load operation, load must be high (1) and enable

must be high or unconnected.

Synchronous parallel load. High (1):

load operation; low (0): shift

operation.

No

load

Clears the q[] outputs. If both sset and sclr

are used and both are asserted, sclr is

dominant. sclr signal affects q[] outputs

before polarity is applied to ports.

Synchronous clear input.

No

sclr

LPM_SHIFTREG Megafunction

Altera Corporation

Feedback

UG-033105

Ports and Parameters

12

2013.03.05