8 tsi to serdes converter block (tsi2serblk), Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 215

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

215

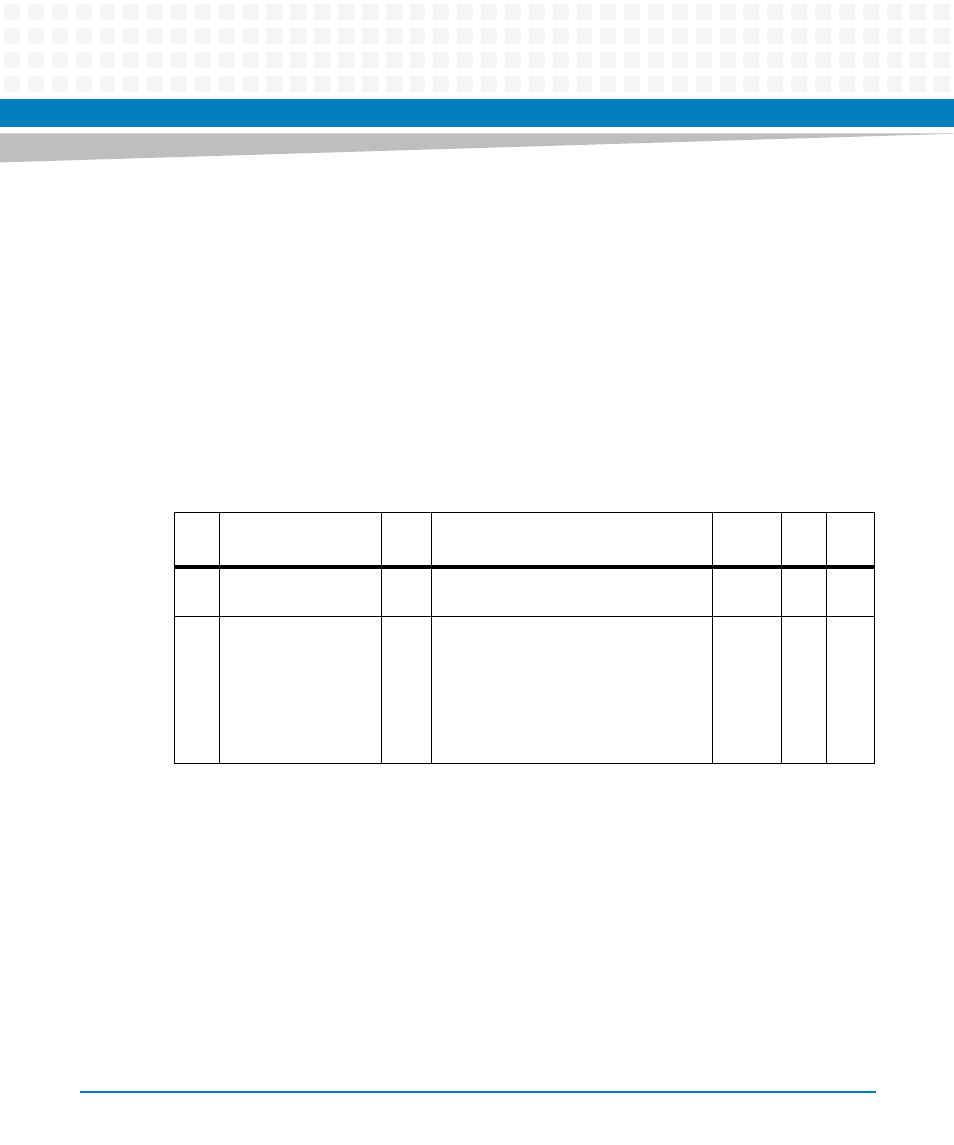

9.5.2.7.6 Test Pattern Comparator Error Count Register

Addresses:

0x10CC, TstPatCmpErrorCntReg0

0x10EC, TstPatCmpErrorCntReg1

Width: 32 bit

After synchronization of the static pattern or the PRBS receiver this registers counts bit errors.

The counter sticks at 0xFFFFFF.

It is cleared, when TstPatCmpRxPatEn bit changes from 0 to 1. i.e. the receiver is re-enabled

again.

9.5.2.8

Tsi to Serdes Converter Block (Tsi2SerBlk)

Resets:

Pwr = Power On Reset

Soft = Soft Reset

The Tsi2SerBlk contains 3 converter blocks to Serdes links to DspFpgas. Each converter can pick

the payload information of up to 30720 outgoing timeslots of the TSI and transfer them to a

DspFpga at the opposite side.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31..

.24

-

-

reserved

undef

-

-

23..

.0

TstPatCmpErrCnt

R

Bit error count. The count keeps its

status after the receiver is stopped,

thus showing its value during the last

measurement.The count cleared, when

TstPatCmpRxPatEn bit changes from 0

to 1. i.e. the receiver is re-enabled

again.

0x0

F

F