Hardware installation, Lpc connector – DFI COM330-B User Manual

Page 38

Advertising

38

2

Hardware Installation

1

ON

4

5

1

ON

4

5

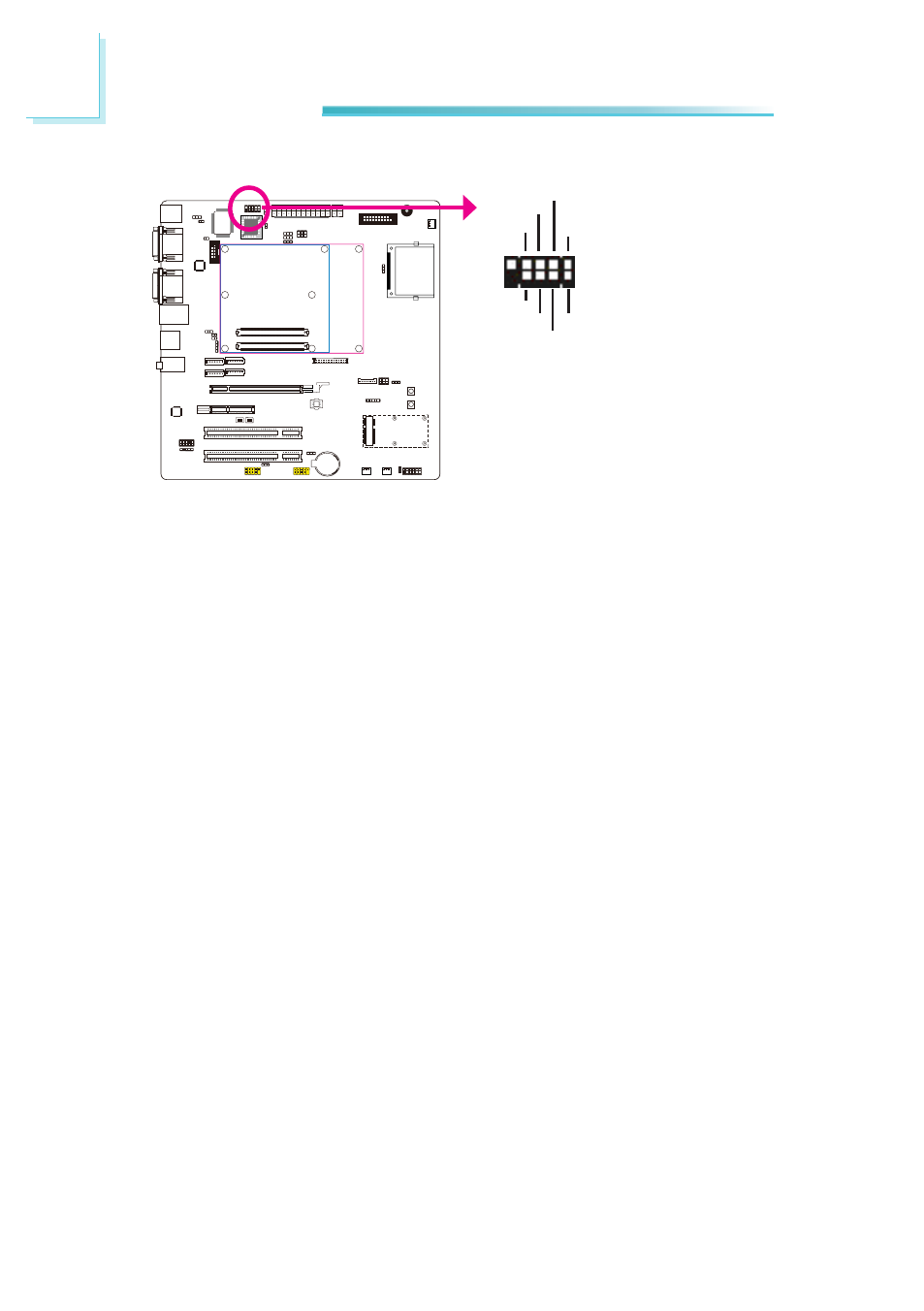

LPC connector

The Low Pin Count Interface was defined by Intel

®

Corporation to facilitate the in-

dustry’s transition towards legacy free systems. It allows the integration of low-

bandwidth legacy I/O components within the system, which are typically provided

by a Super I/O controller. Furthermore, it can be used to interface firmware hubs,

Trusted Platform Module (TPM) devices and embedded controller solutions. Data

transfer on the LPC bus is implemented over a 4 bit serialized data interface, which

uses a 33MHz LPC bus clock. For more information about LPC bus refer to the Intel

®

Low Pin Count Interface Specification Revision 1.1’.

VCC3

LAD0

LAD1

GND

LAD3

RST#

FRAME#

CLK

1

9

2

LAD2

Advertising

This manual is related to the following products: