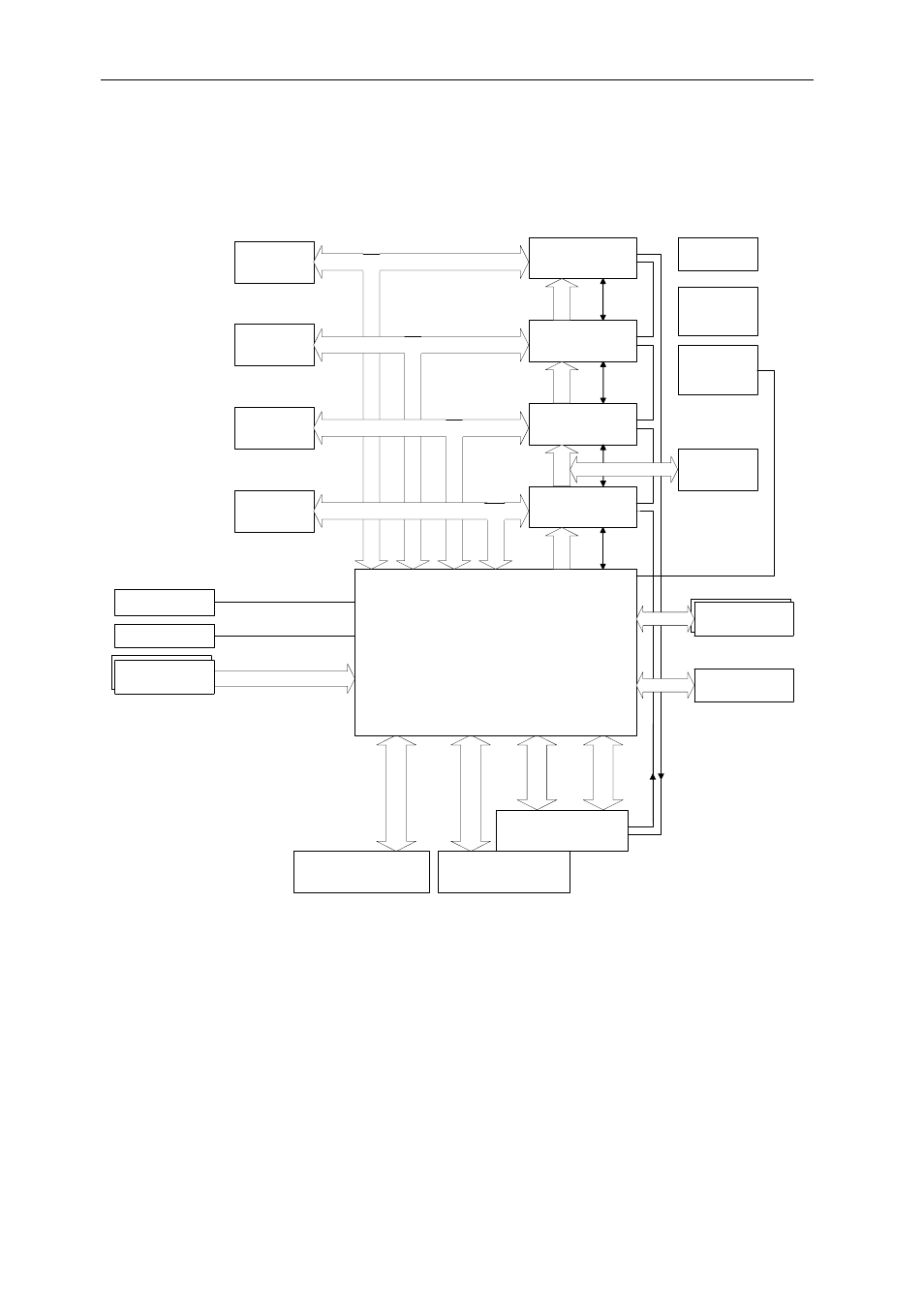

Block diagram, Fpga (xc2vp70) – Sundance SMT395Q User Manual

Page 7

Advertising

Version 1.0.7

Page 7 of 31

SMT395Q User Manual

Block Diagram

120 I/O Pins; 16-bit Data

2x

Comm

-P

or

ts

2

4 I/O

pin

s

Tim

er &

Con

tr

ol

2x Comm-

P

or

ts

24

I/

O

pins

Glob

al

B

us

74

I/

O

pins

FPGA

(XC2VP70)

VirtexII-Pro, FF1704

996 I/O Pins

1.5V

'C64xx

DSP

JTAG Header

J1 Top Primary TIM

Connector

Comm-Port 0 & 3

J3 Global Expansion

Connector

J2 Bottom Primary TIM

Connector

Comm-Port 1 & 4

8 LEDs &

4 I/O pins

Flash (CE1)

64Mbit

Oscillators

voltage

convertors

1.5V & 1.2V

Sundance High-

Speed Bus

60-way x2

'C64xx

DSP

'C64xx

DSP

'C64xx

DSP

HPI

HPI

HPI

HPI

Serial

port

16

bi

t

EMI

F

A

E

M

IFA

EMI

F

A

E

MI

F

A

64

bit

64

bit

64

bit

64

bit

EMIFB

EMIFB

EMIFB

A

B

C

D

DRAM

64Mbytes

DRAM

64Mbytes

DRAM

64Mbytes

DRAM

128Mbytes

Sundance RSL

x14

JTAG

chain

256Mbytes

DDR memory

Power

monitoring

Advertising