Architecture description, Tms320c6416t, Architecture description tms320c6416t – Sundance SMT395Q User Manual

Page 8

Version 1.0.7

Page 8 of 31

SMT395Q User Manual

Architecture Description

The SMT395Q TIM consists of 4 Texas Instruments TMS320C6416Ts running at up to

1GHz. Modules are populated with 320MBytes of SDRAM for the DSPs, and 256Mbytes of

DDR memory for the FPGA.

A Field Programmable Gate Array (FPGA) is used to manage global bus accesses and

implement four ComPorts and two Sundance High Speed Buses. This is a Xilinx Virtex-II Pro

device.

TMS320C6416T

These processors will run with zero wait states from internal SRAM.

An on-board crystal oscillator provides the clock used for the C60. Alternatively an on-board

clock synthesiser provides the clock for the C60 (build option). The synthesiser frequency

can be altered under DSP control. These clocks are multiplied by 20 by the DSP.

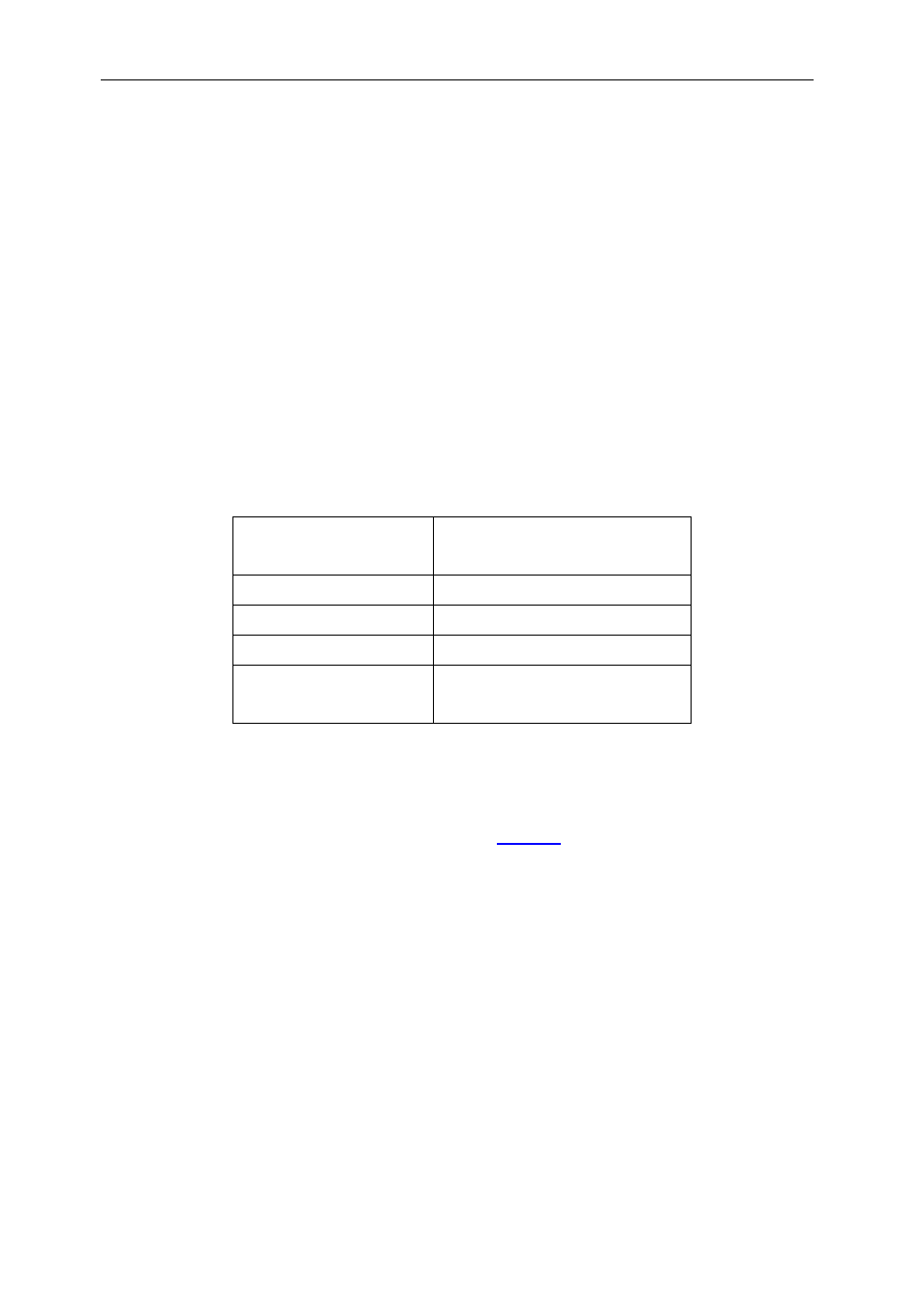

The following table shows the main DSP characteristics.

Features C6416T

DMA / McBSP / Timer

64/3/3

On-chip memory

1056KB

Speed 1GHz

Others UTOPIA

Viterbi and Turbo decoders

The SMT395Q implementation using this DSP provides interfaces using the EMIFs (External

Memory Interfaces A & B), timers and JTAG.

The JTAG interface is provided to enable application debugging via a suitable JTAG

controller and software. Typically, this will be an

and TI Code Composer Studio.

This is an invaluable interface which enables the application programmer to quickly debug a

‘chain’ of processors in single or multi-processor situations.

The EMIF_A is used to connect to a 120MHz, 64MB bank of SDRAM (128MB for DSP_A,

and the VirtexII-Pro).

The flash (DSP_A only) is connected via EMIF_B as a 16-bit device. The EMIF_A supplies 4

‘chip selects’ which are used for these selections.