Avago Technologies LSI53C1000R User Manual

Page 251

Advertising

Block Move Instructions

5-9

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

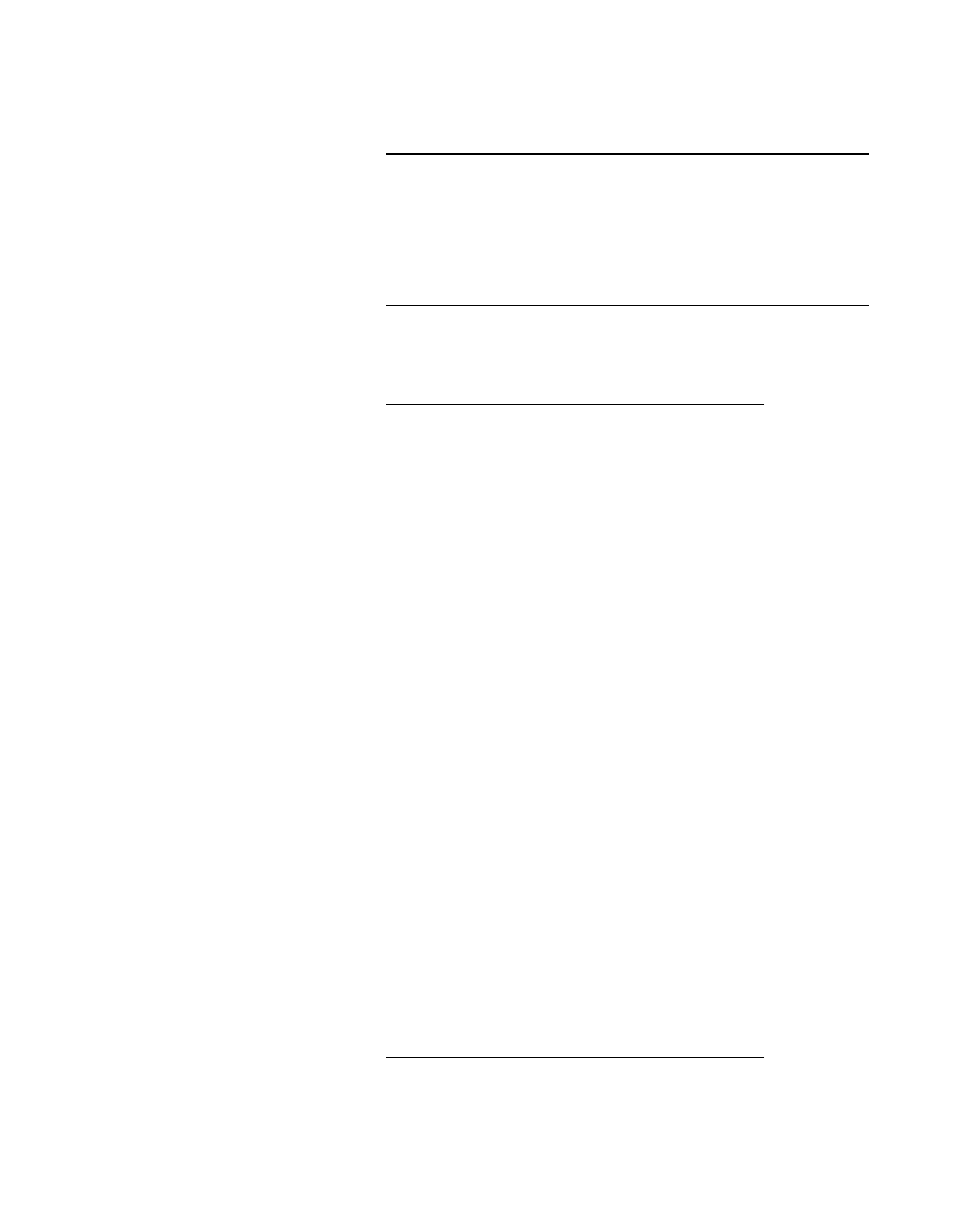

Table Indirect Index mode mapping:

EN64TIBMV 64TIMOD

Upper 32-Bit Data

Address Comes From

0

0

SBMS

0

1

SBMS

1

0

ScratchC–J, MMWS, MMRS, SFS,

DRS, SBMS, DBMS

1

1

1st Table Entry Dword bits [31:24]

(40-bit addressing only)

Index Value

Selector Used

0x00

Scratch C

0x01

Scratch D

0x02

Scratch E

0x03

Scratch F

0x04

Scratch G

0x05

Scratch H

0x06

Scratch I

0x07

Scratch J

0x08

Scratch K

0x09

Scratch L

0x0A

Scratch M

0x0B

Scratch N

0x0C

Scratch O

0x0D

Scratch P

0x0E

Scratch Q

0x0F

Scratch R

0x10

MMRS

0x11

MMWS

0x12

SFS

0x13

DRS

0x14

SBMS

0x15

SBMS

0x16–0x1F

Illegal (Results in an IID interrupt)

Advertising

This manual is related to the following products: