Data computation – Altera Nios II C2H Compiler User Manual

Page 62

3–22

9.1

Altera Corporation

Nios II C2H Compiler User Guide

November 2009

Memory Accesses

port. After some number of clock cycles determined by the slave memory

latency and arbitration delay, valid

readdata

returns to the master port.

(See section

“Read Operations with Latency” on page 3–37

.)

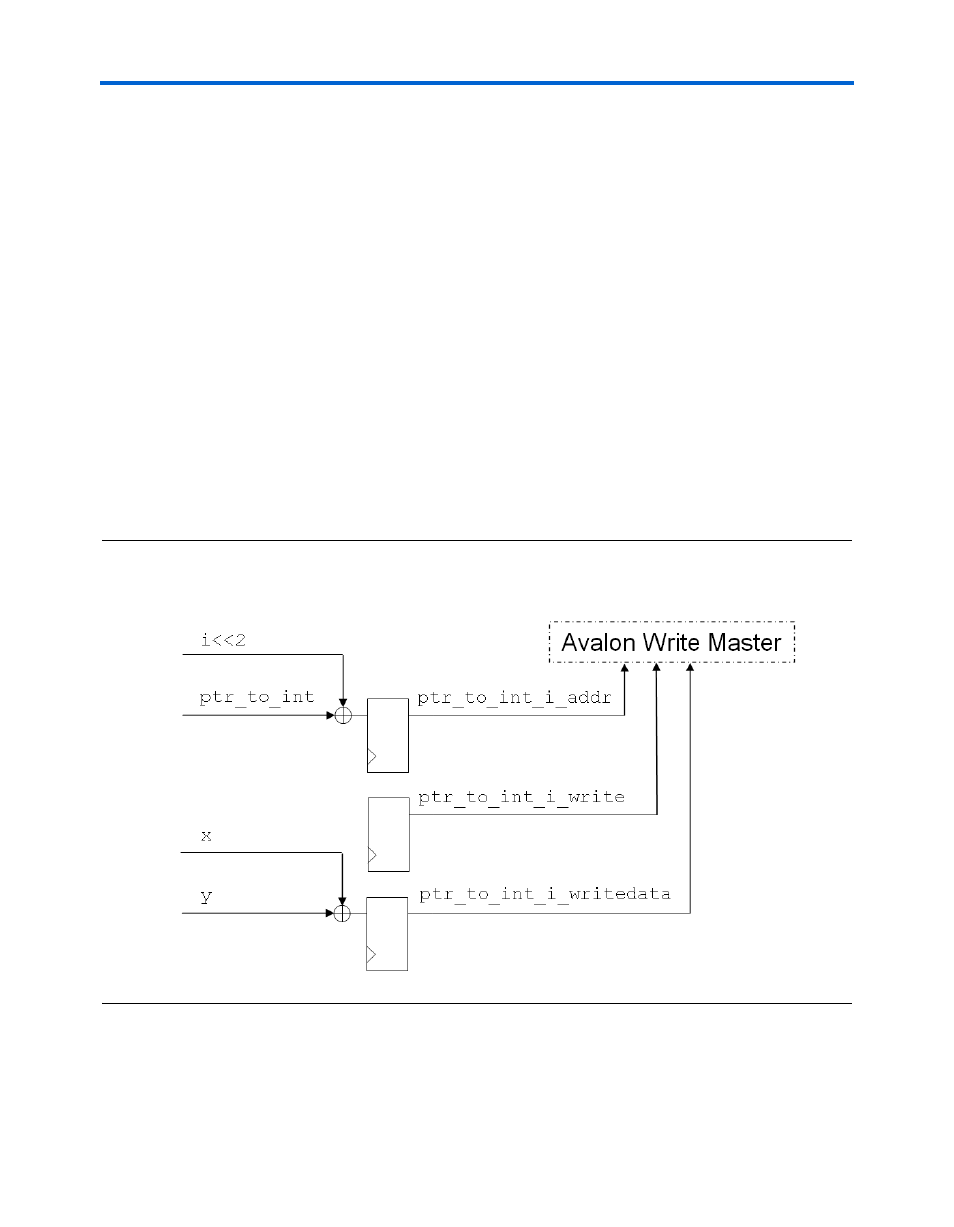

Data Computation

For write operations to dereferenced pointers, data-computation logic in

the accelerator computes the value of the expression to write to memory.

This value is the write-data for an Avalon-MM master transfer to

memory. Data-computation logic operates in parallel with the address-

computation logic.

Consider the pointer dereference in the following code which performs a

write operation:

*(ptr_to_int + i) = x + y;

shows an example of the logic created for this pointer

dereference for a write operation.

Figure 3–10. Data Generation for a Write Operation