Altera Nios II C2H Compiler User Manual

Page 98

4–4

9.1

Altera Corporation

Nios II C2H Compiler User Guide

November 2009

Resources

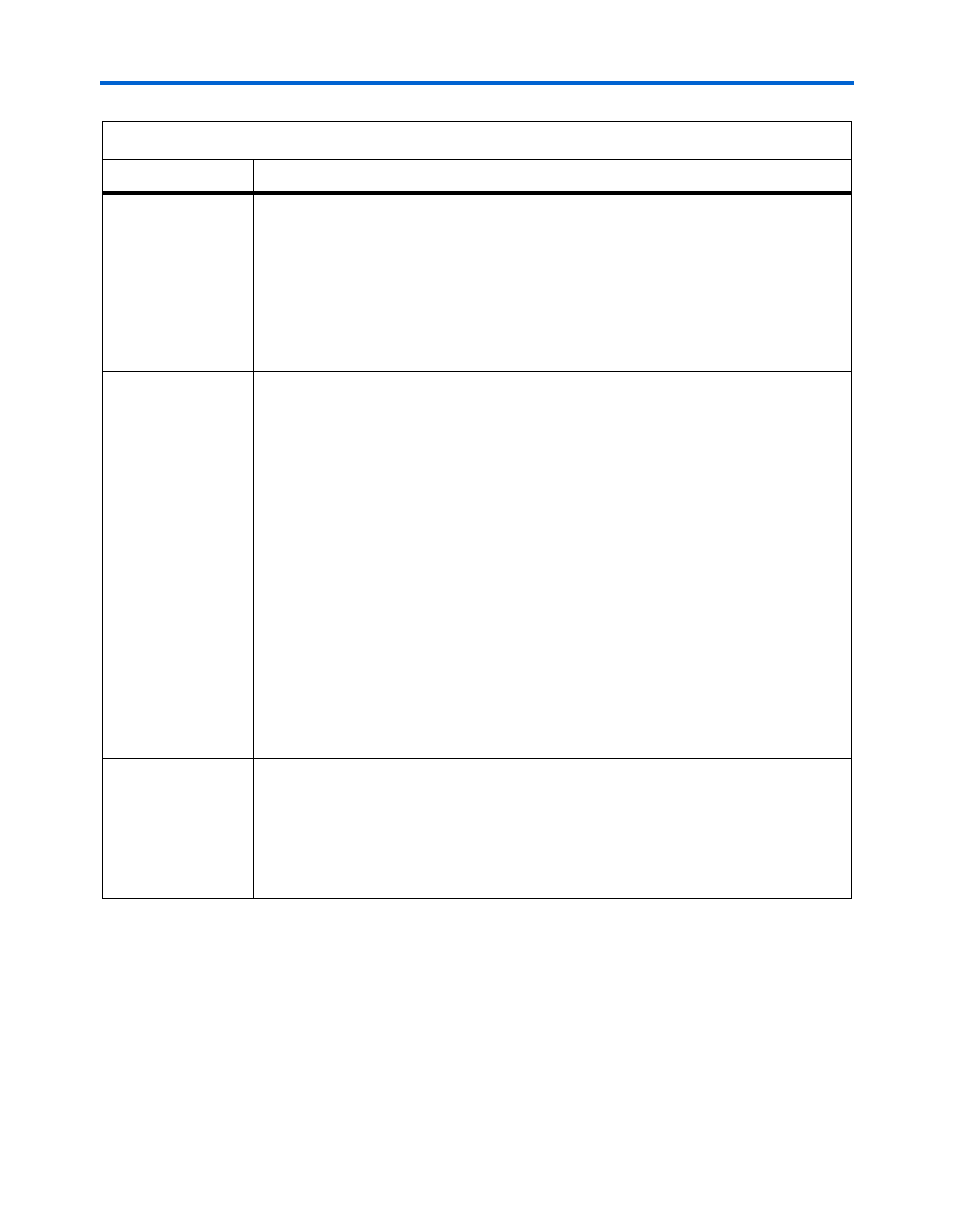

Table 4–2. Function Build Configurations

Configuration

Meaning

Use hardware

accelerator in place

of software

implementation.

Flush data cache

before each call

Use this configuration if you are not certain whether cache coherency is an issue in your

system.

In this configuration, every time the software calls the accelerated function, the wrapper

function flushes the entire Nios II data cache, to prevent cache coherency issues. The

C2H Compiler inserts flush code into the wrapper function so no source code modification

is necessary. Since flushing the cache is a fixed overhead, if you have strict processing

time requirements you need to study the system architecture and determine if this

operation is necessary.

Use hardware

accelerator in place

of software

implementation

This configuration uses the hardware accelerator without flushing the data cache before

each invocation. Use this configuration with algorithms that do not require Nios II data

cache flushing.

Do not use this configuration if you have not studied your algorithm to determine if it could

have cache coherency problems. The accelerated function might create cache coherency

problems in certain corner cases. To prevent cache coherency problems, use one or more

of the following techniques in your code:

●

Allocate all shared data in uncached Nios II memory space. Refer to “

Bit-31 Cache

Bypass”

in the

.

●

Flush all shared data before calling the accelerated function.

●

Place all shared data in a tightly coupled memory.

●

Manage cache coherency in a multiprocessor system by establishing a cache

coherency protocol between the processor controlling the accelerated function and all

other processors.

●

Use cache bypass macros to access all shared data.

●

Do not share memory between the hardware accelerator and the Nios II processor

●

Refer

chapter of the

to learn more about cache coherency.

Use software

implementation

Much like the project wide configuration, this causes the C2H Compiler to link the

software implementation of the accelerated function. Unlike the project wide

configuration, this only affects a single accelerated function and not the entire software

project. You can use this configuration to prototype changes to your algorithm without

having to regenerate or recompile the hardware. This project configuration does not

remove the existing accelerator from the system.

Note to

:

(1)

Use caution passing uncached pointers to a C2H accelerator. There are two unusual situations that require special

consideration: (a) If the accelerator performs direct arithmetic or comparisons on the address value of a pointer, it

must account for the possibility that bit 31 is set. (b) If the accelerated function masters a component whose true

address is >=

0x80000000

, and uses the same Avalon-MM master port to connect to the memory that it shares

with the Nios II processor, uncached pointers to the shared memory might result in spurious Avalon-MM transfers

to addresses >=

0x80000000

.