Altera Nios II C2H Compiler User Manual

Page 87

Altera Corporation

9.1

3–47

November 2009

Nios II C2H Compiler User Guide

C-to-Hardware Mapping Reference

that performs Avalon-MM pipelined read transfers. Inside the

accelerator, the master port connects to a FIFO, which guarantees the

accelerator can receive data for all pending read transfers, regardless of

whether the state machine stalls.

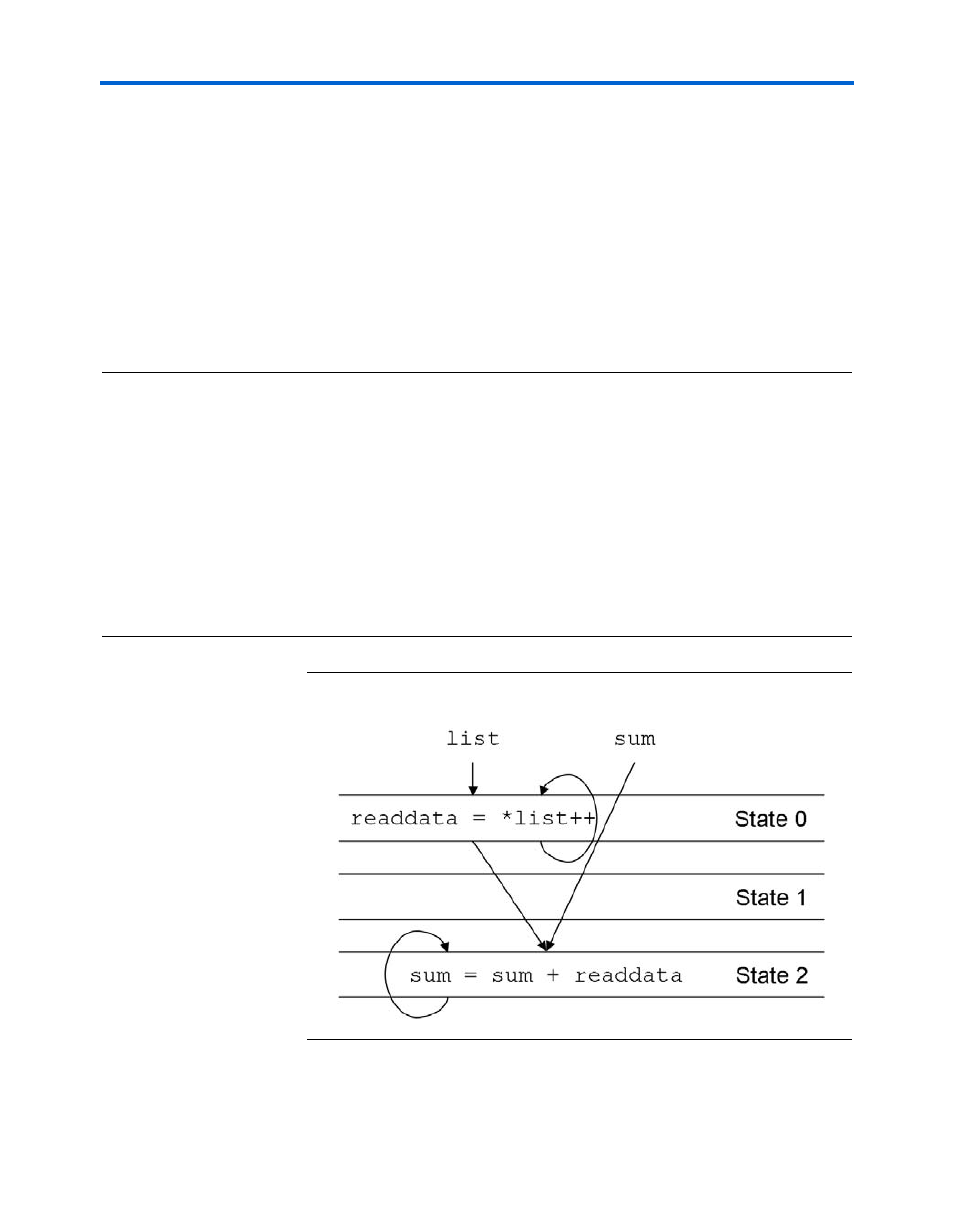

shows the dependency graph for

, which

demonstrates a loop that pipelines memory accesses with latency. This

example uses the connection pragma to connect the master port for

variable

list

to a slave memory named

my_mem_with_two_cycles_read_latency

, as described in section

“Master-Slave Connections” on page 3–23

Example 3–37. Accessing Memory with Latency

#pragma altera_accelerate connect_variable \

sum_elements/list to \

my_mem_with_two_cycles_read_latency

int sum_elements (int *list, int len)

{

int i;

int sum = 0;

for (i=0; i<len; i++)

sum += *list++;

}

Figure 3–24. Accessing Memory with Latency