Altera SDI II MegaCore User Manual

Page 13

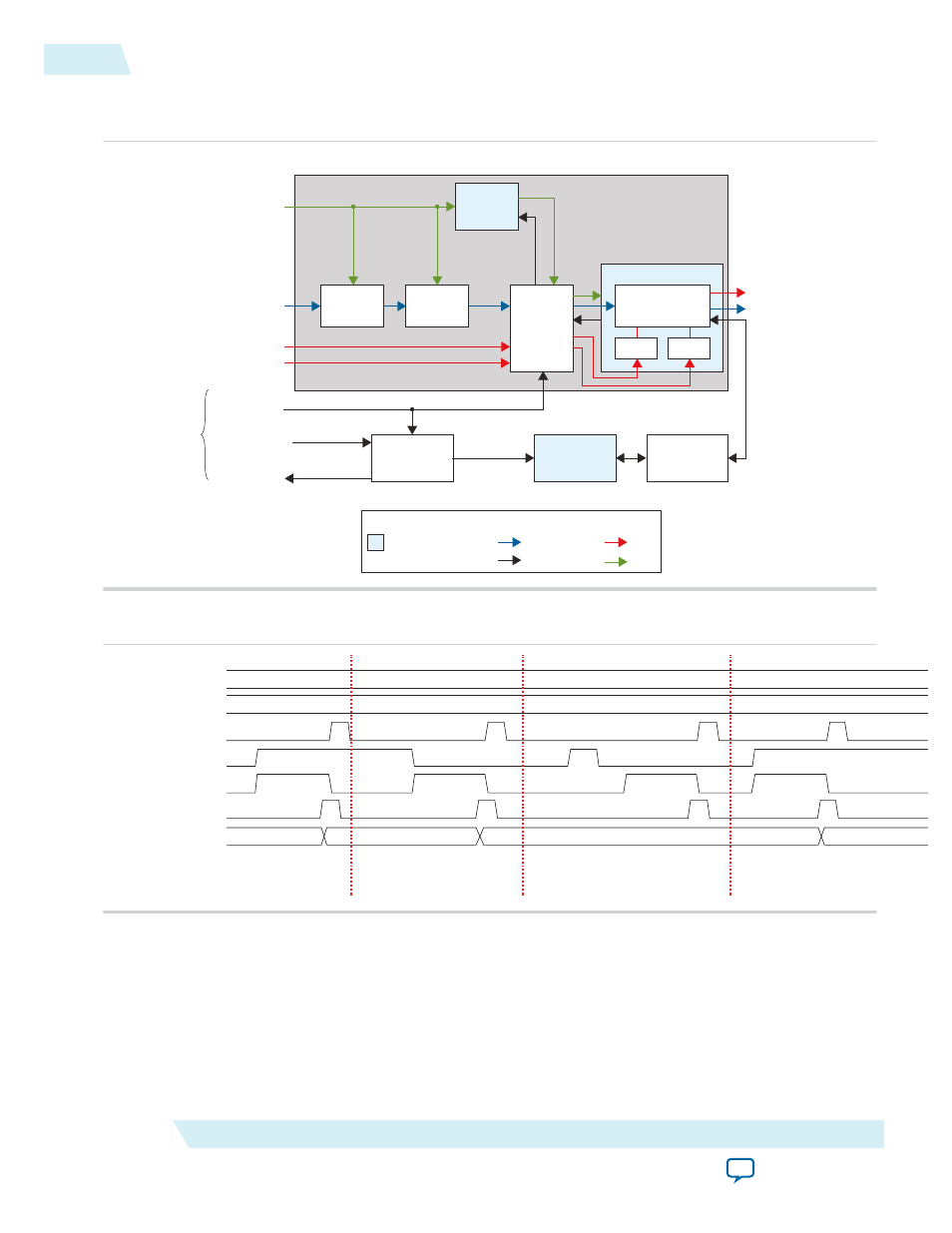

Figure 2-7: Hardware Implementation of the Dynamic TX Clock Switching Feature

The figure shows the TX clock switching feature with two TX PLLs.

TX Protocol

TX PHY

Management

PHY Adapter

Transceiver

PHY Reset

Controller

Transceiver

Reconfiguration

Controller

Reconfiguration

Management

Reconfiguration

Router

TX Transceiver

Channel

TX PLL0

TX PLL1

Parallel Video In

(tx_datain and

tx_datain_b for

HD-SDI Dual Link)

Primary Reference Clock (xcvr_refclk)

Alternative Reference Clock (xcvr_refclk_alt)

Reset

(tx_rst)

Tx PLL Switching

Handshaking

Signals

Reconfiguration Acknowledge

(ch1_{tx/du}_tx_reconfig_done)

Reconfiguration Request

(ch1_{tx/du}_tx_start_reconfig)

TX PLL Select (ch1_{tx/du}_tx_pll_sel)

Avalon-MM

Control Interface

TX Clock Out (tx_clkout)

(148.5 or 148.35 MHz)

SDI Out

(sdi_tx and sdi_tx_b for

HD-SDI Dual Link)

Altera Transceiver

Analog Reset

Digital Reset

PLL Powerdown

PLL Locked

Cal Busy

TX PLL Select

SDI TX (All Video Standard Modes except SD-SDI)

Altera PHY

IP Core

Data

Control/Status

Clock

Reset

Legend

Figure 2-8: Dynamic TX Clock Switching Timing Diagram

148.5 MHz

148.35 MHz

148.5 MHz

Case 1

Case 2

Case 3

148.35 MHz

148.5 MHz

148.35 MHz

xcvr_refclk

xcvr_refclk_alt

tx_rst

ch1_{tx/du}_tx_pll_sel

ch1_{tx/du}_tx_start_reconfig

ch1_{tx/du}_tx_reconfig_done

tx_clkout

The table below describes the behavior of the dynamic switching feature when you initiate a handshaking

process (with reference to the timing diagram).

2-8

Dynamic TX Clock Switching

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Overview