Reconfiguration management parameters, Reconfiguration management parameters -26 – Altera SDI II MegaCore User Manual

Page 41

Related Information

•

Transceiver Reconfiguration Controller

on page 3-15

The transceiver reconfiguration controller reconfigures the transceivers. The transceiver reconfiguration

controller in the Arria V, Cyclone V, and Stratix V design examples and the Arria 10 design example is

used differently.

•

Modifying the Transceiver Reconfiguration Controller

•

More information about the transceiver reconfiguration controller frequency range.

Reconfiguration Management Parameters

Table below lists the parameters for reconfiguration management.

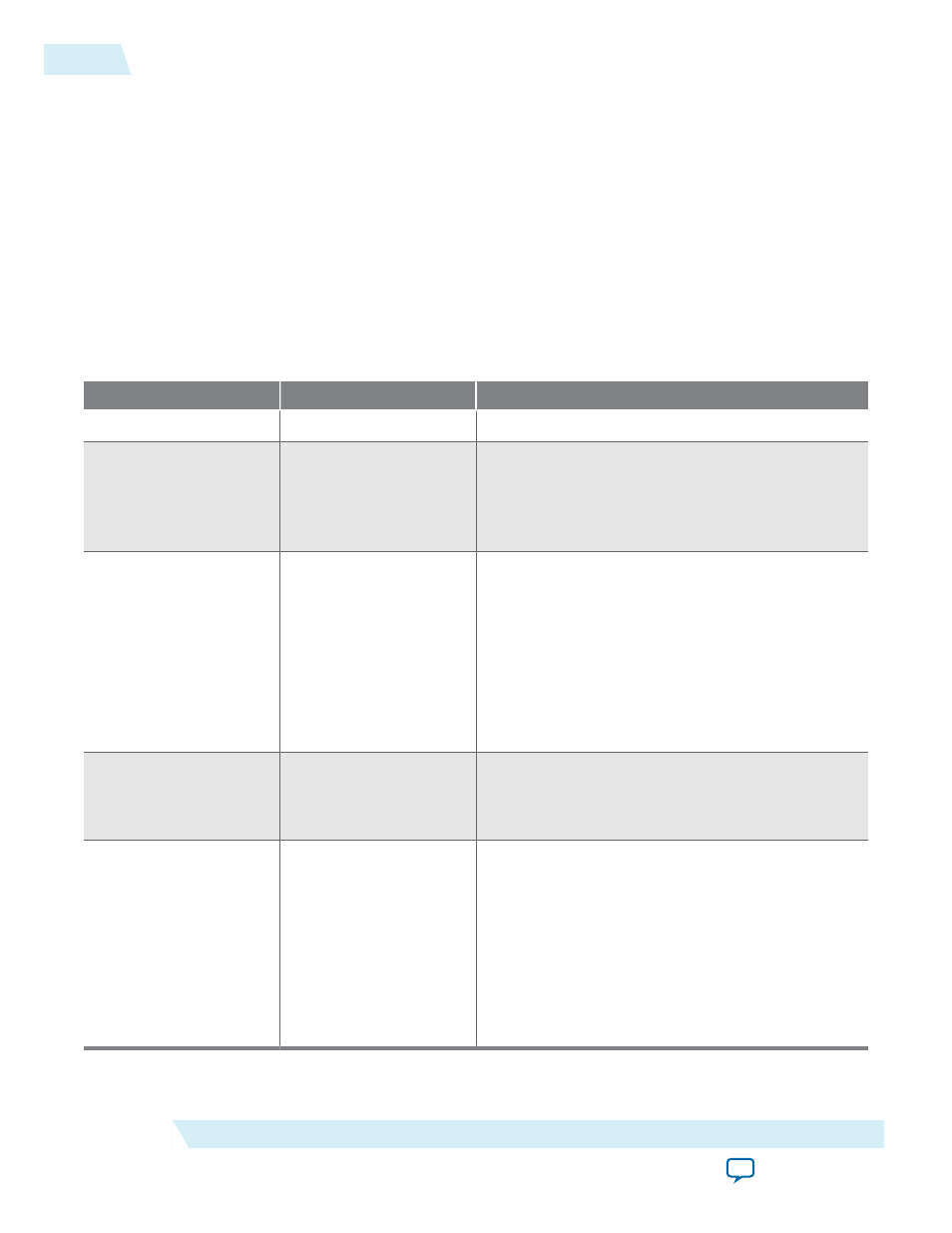

Table 3-11: Reconfiguration Management Parameters

Parameter

Value

Description

NUM_CHS

1 (minimum)

Number of channels required to do reconfiguration

FAMILY

• Arria V

• Arria V GZ

• Cyclone V

• Stratix V

Supported device family

DIRECTION

• tx

• rx

• du

Direction of the core selected in the parameter

editor. This parameter affects the logical channel

number assigned in the generated example design.

If you are making any changes to the design, please

ignore this parameter and assign the logical channel

number correctly.

Refer to Expanding to Multiple Channels section to

know how to assign the logical channel number.

VIDEO_STANDARD

• tr

• dl

Current video standard.

Specify dl for HD dual-link or tr for other

standards.

XCVR_TX_PLL_SEL

• 1

• 2

The selected method to perform TX PLL reconfigu‐

ration for dynamic clock switching. Specify 1 to

switch TX PLLs or 2 to switch TX PLL reference

clocks.

The specified value must match the parameter value

you select when you instantiate the core.

Refer to Dynamic TX Clock Switching section to

know more about clock switching.

3-26

Reconfiguration Management Parameters

UG-01125

2015.05.04

Altera Corporation

SDI II IP Core Getting Started