Altera SDI II MegaCore User Manual

Page 75

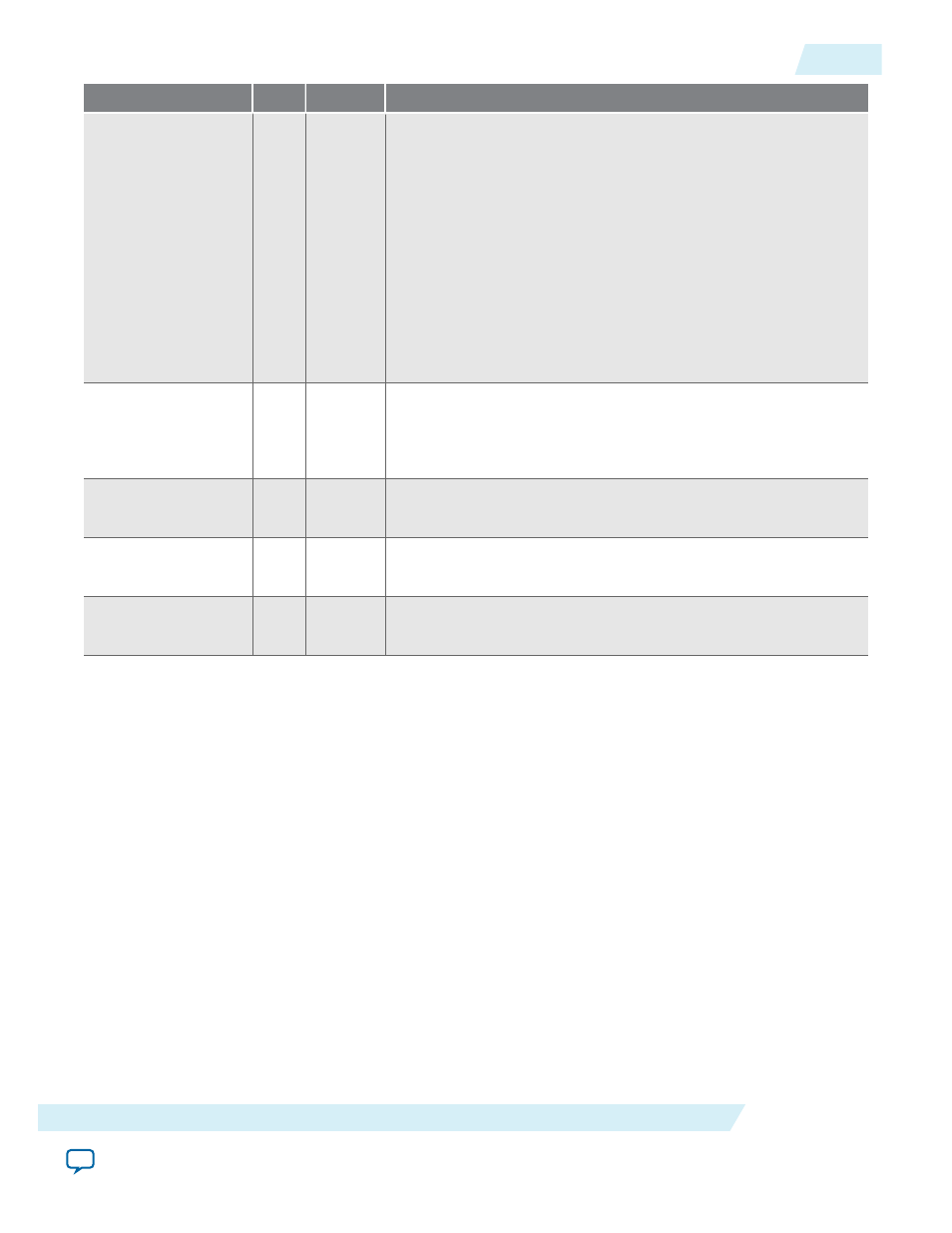

Signal

Width Direction

Description

rx_dataout_valid

1

Output

Data valid from the oversampling logic. The receiver asserts this

signal to indicate current data on

rx_dataout

is valid. The

timing (H: High, L: Low) for each video standard has the

following settings:

• SD-SDI = 1H 4L 1H 5L

• HD-SDI = H

• 3G-SDI = H

• HD-SDI Dual Link = H

• Dual standard = SD (1H 4L 1H 5L); HD (H)

• Triple standard = SD (1H 4L 1H 5L); HD (H); 3G (H)

• Multi standard (up to 12G) = SD (1H 4L 1H 5L); HD (1H 1L);

3G/6G/12G (H)

rx_f

1

Output

Field bit timing signal. This signal indicates which video field is

currently active. For interlaced frame, 0 means first field (F0)

while 1 means second field (F1). For progressive frame, the value

is always 0.

rx_v

1

Output

Vertical blanking interval timing signal. The receiver asserts this

signal when the vertical blanking interval is active.

rx_h

1

Output

Horizontal blanking interval timing signal. The receiver asserts

this signal when the horizontal blanking interval is active.

rx_ap

1

Output

Active picture interval timing signal. The receiver asserts this

signal when the active picture interval is active.

UG-01125

2015.05.04

SDI II IP Core Signals

4-33

SDI II IP Core Functional Description

Altera Corporation