Altera SDI II MegaCore User Manual

Page 28

Advertising

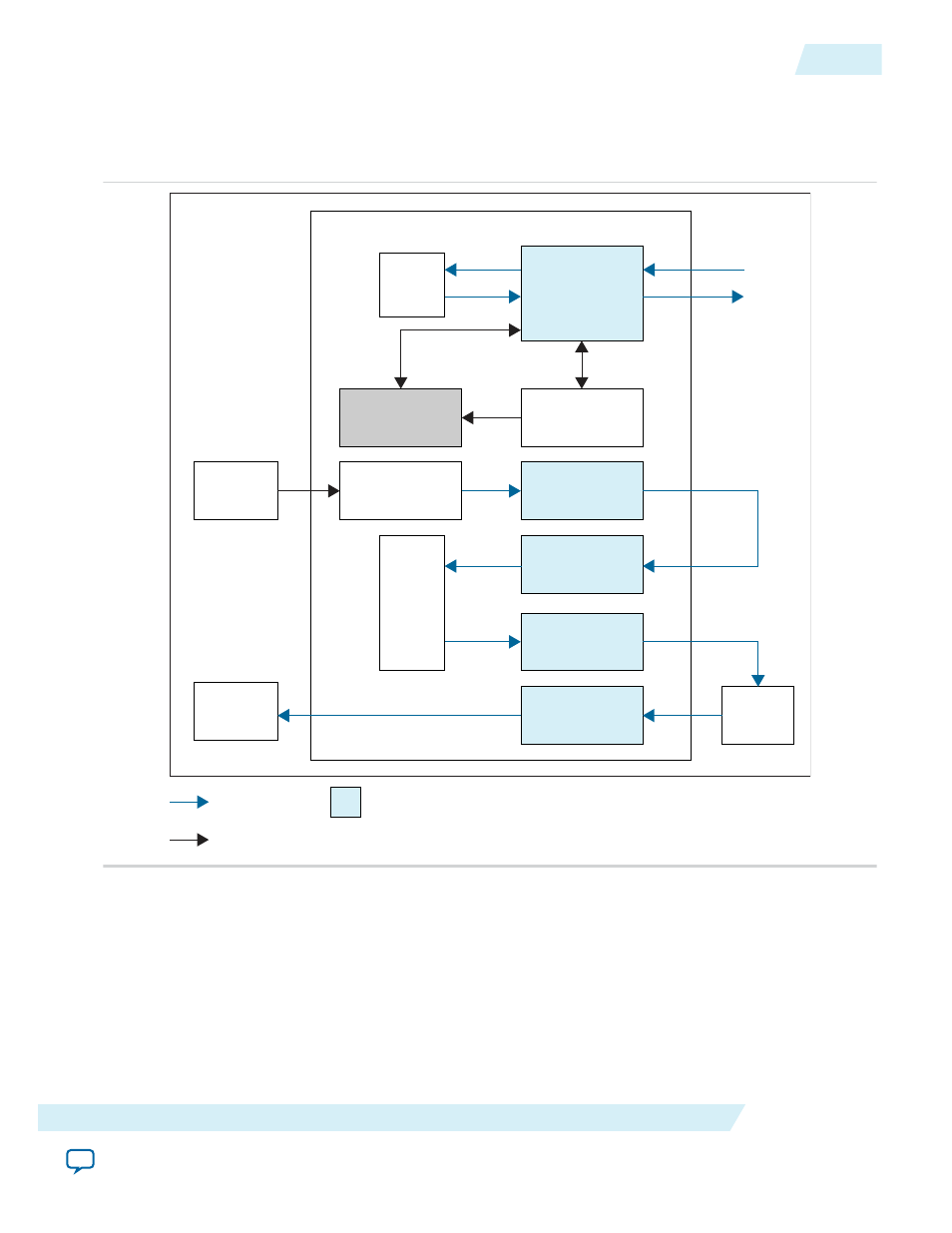

Figure 3-3: Design Example Entity and Simulation Testbench for HD-SDI Dual Link to 3G-SDI (Level B)

Conversion

The figure below illustrates the generated design example entity and simulation testbench when you

generate HD-SDI dual link receiver with Convert HD-SDI dual link to 3G-SDI (level B) option enabled.

Loopback

Path

Ch0

Loopback

(SDI Duplex)

Reconfiguration

Management/Router

Ch1 Test

(HD DL SDI TX)

Ch1 DUT

(HD DL SDI RX)

A to B

Video Pattern

Generator

Test

Control

Ch2 Test

(3-Gb SDI TX)

Ch2 Test

(3-Gb SDI RX)

TX

Checker

RX

Checker

Loopback

Path

Data

Control

SDI II IP Core

Design Example

Testbench

Transceiver

Reconfiguration

Controller

UG-01125

2015.05.04

Design Examples for Arria V, Cyclone V, and Stratix V Devices

3-13

SDI II IP Core Getting Started

Altera Corporation

Advertising