Altera Arria V Hard IP for PCI Express User Manual

Page 37

Chapter 3: Getting Started with the Avalon-MM Arria Hard IP for PCI Express

3–3

Customizing the Arria V Hard IP for PCI Express IP Core

December 2013

Altera Corporation

Arria V Hard IP for PCI Express

User Guide

Customizing the Arria V Hard IP for PCI Express IP Core

The parameter editor uses bold headings to divide the parameters into separate

sections. You can use the scroll bar on the right to view parameters that are not

initially visible. Follow these steps to parameterize the Hard IP for PCI Express IP

core:

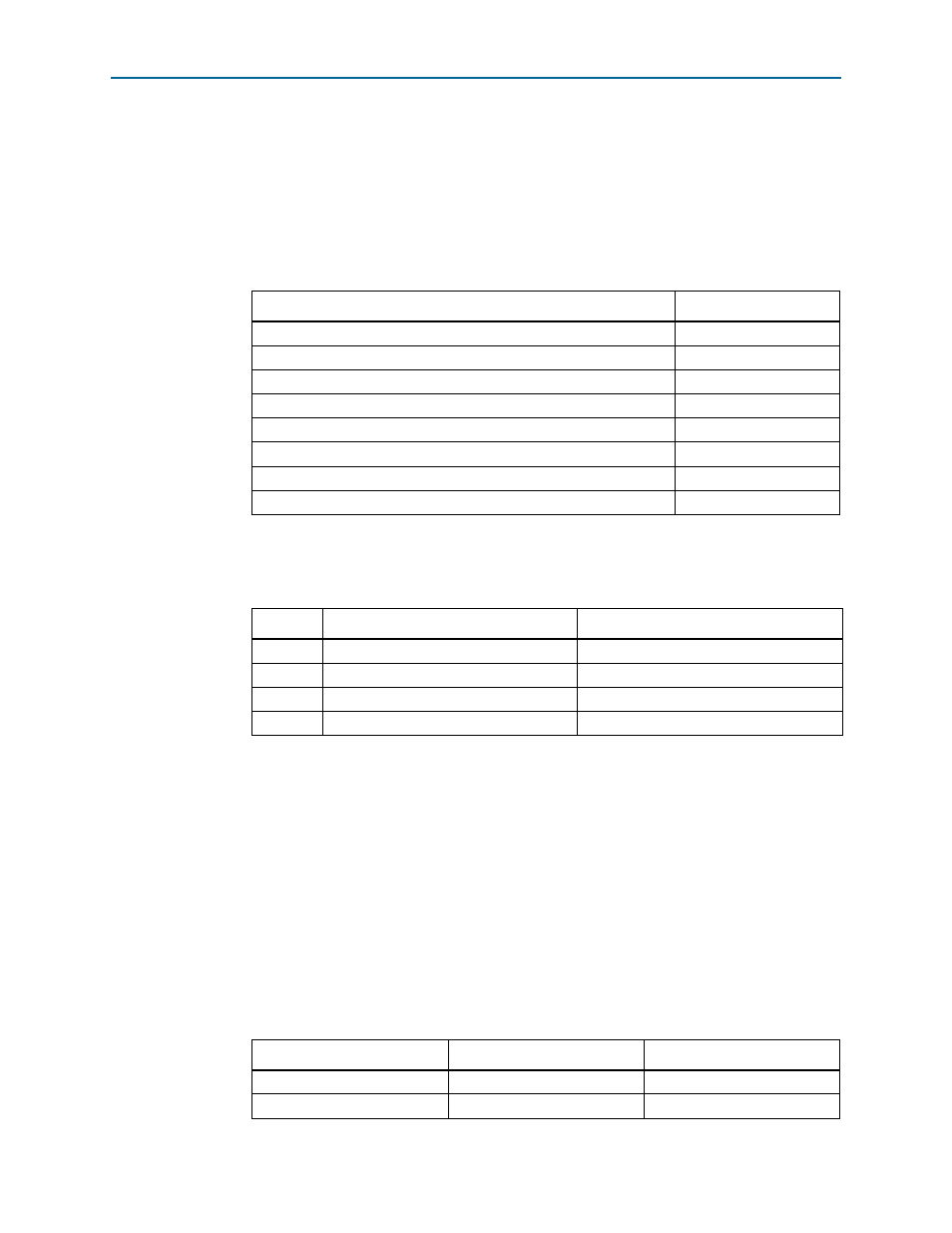

1. Under the System Settings heading, specify the settings in

2. Under the PCI Base Address Registers (Type 0 Configuration Space) heading,

specify the settings in

Table 3–3

.

1

For existing Qsys Avalon-MM designs created in the Quartus II 12.0 or earlier release,

you must re-enable the BARs in 12.1.

For more information about the use of BARs to translate PCI Express addresses to

Avalon-MM addresses, refer to

“PCI Express-to-Avalon-MM Address Translation

for Endpoints for 32-Bit Bridge” on page 7–20

. For more information about

minimizing BAR sizes, refer to

“Minimizing BAR Sizes and the PCIe Address

Space” on page 7–21

.

3. For the Device Identification Registers, specify the values listed in the center

column of

Table 3–4

. The right-hand column of this table lists the value assigned to

Altera devices. You must use the Altera values to run the Altera testbench. Be sure

to use your company’s values for your final product.

Table 3–2. System Settings

Parameter

Value

Number of lanes

×4

Lane rate

Gen1 (2.5 Gbps)

Port type

Native endpoint

RX buffer credit allocation – performance for received requests

Low

Reference clock frequency

100 MHz

Use 62.5 MHz application clock

Off

Enable configuration via the PCIe link

Off

ATX PLL

Off

Table 3–3. PCI Base Address Registers (Type 0 Configuration Space)

BAR

BAR Type

BAR Size

0

64-bit Prefetchable Memory

0

1

Not used

0

2

32 bit Non-Prefetchable

0

3–5

Not used

0

Table 3–4. Device Identification Registers (Part 1 of 2)

Parameter

Value

Altera Value

Vendor ID

0x00000000

0x00001172

Device ID

0x00000001

0x0000E001