Mechanical and connector information – Artesyn RTM-ATCA-736x-DD Installation and Use (June 2014) User Manual

Page 53

Mechanical and Connector Information

RTM-ATCA-736X-DD Installation and Use (6806800L82C)

53

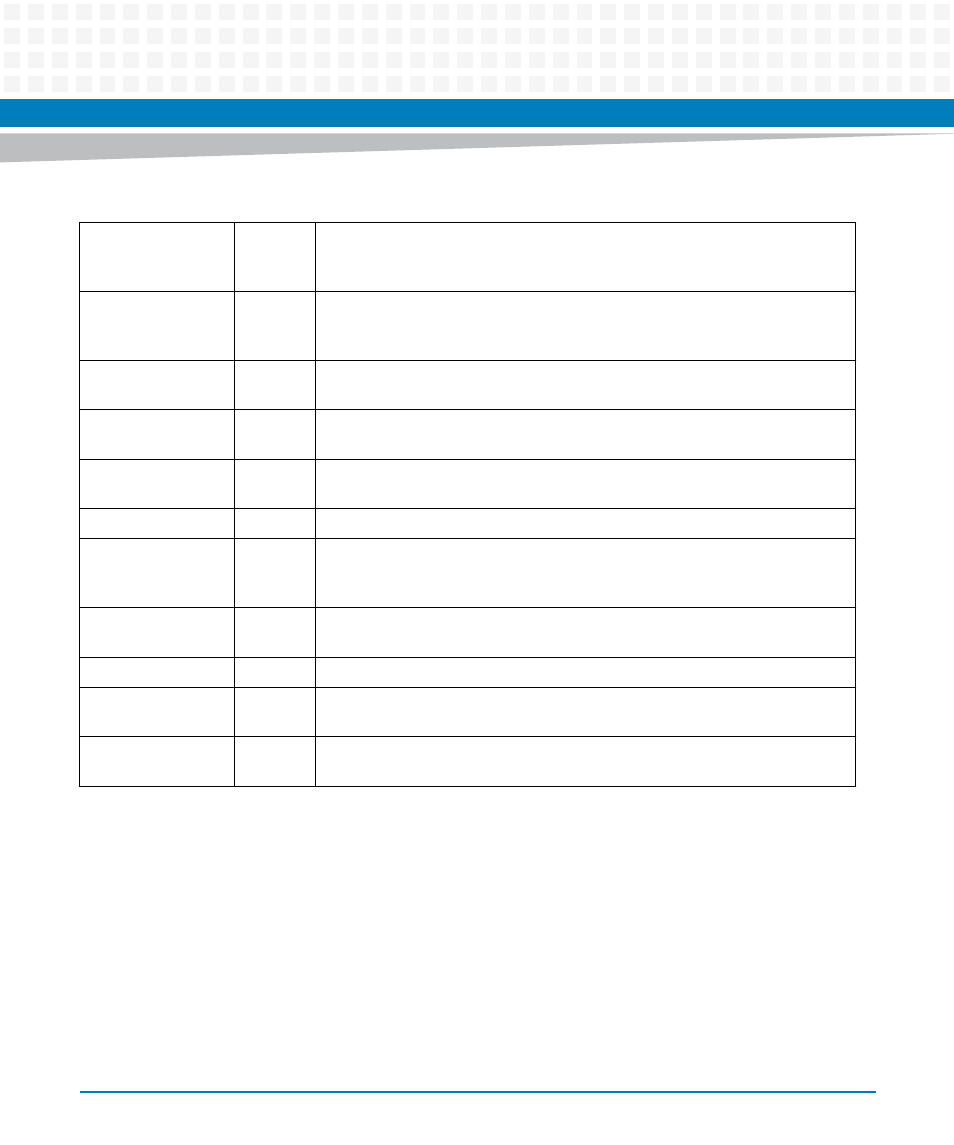

4.2.2.3

Connector J32, PCI-Express and Test Infrastructure Pin Assignments

The RTM-ATCA-736X-DD , J31 connector pin assignments and descriptions appear below.

POWERGOOD

O

Open Drain. When low indicates to RTM that it is fully inserted and that MMC

can start execution. Logic high shall keep MMC in reset state. This signal shall

have a pull-up resistor.

LSI_SAS[ ]

I/O

LVDS. These transceiver pairs connect to the LSI SAS controller, port2 and

port3. Some front blades route these ports to the Zone2 update channel

where additional disks may reside.

DCA1_SAS[]

I/O

LVDS. These transceiver pairs route to the secondary SAS port of the hard drive

located on DCA (drive carrier assembly) #1

DCA2_SAS[]

i/O

LVDS. These transceiver pairs route to the secondary SAS port of the hard drive

located on DCA (drive carrier assembly) #2

SATA[ ]

I/O

(Unused) LVDS. These transceiver pairs are driven by a storage controller on

the host blade.

USB

I/O

(Unused) USB bidirectional, differential data pin pair

TDO, TDI

Test Data In/Out signals as defined in JTAG. The RTM provides a bypass circuit

to propagate this signal and complete the test data chain (that is, TDI connects

to TDO)

P10_Rx, P10_Tx,

P10_Clk100+

(Unused) LVDS. Port #10 PCI express differential signal pairs for transmit

receive and 100MHz reference Clock

88_PCIE_RST

PCIE Reset driven by host blade.

IPMB_SCL,

IPMB_SDA

IPMI/I2C serial-bus clock and data signals, as defined in AMC.0 specification.

VP12

12V Payload Power, enabled after successful E-keying, as outlined in the AMC.0

specification.

Table 4-7 Connector J30, Management Infrastructure Signal Descriptions (continued)