3 signal integrity – Nevion HD-TD-10GMX-6 User Manual

Page 8

HD-TD-10GMX-6 / HD-TD-10GDX-6

Rev. B

nevion.com | 8

As a solution for both these situations the mux and de-mux provides the Sticky error

indication mode. In this mode the error bits will only be cleared when the operator resets

the error counter from the Multicon Info page. The error counters will still only count the

number of fields or frames that actually contains errors. This way it is possible to diagnose

the error even a long time after the error situation has been rectified. Note however that if

several errors have occurred since the last counter reset it will not be possible to tell when

or for how long each was present, or if they occurred at the same time or not.

3.1.3 Signal integrity

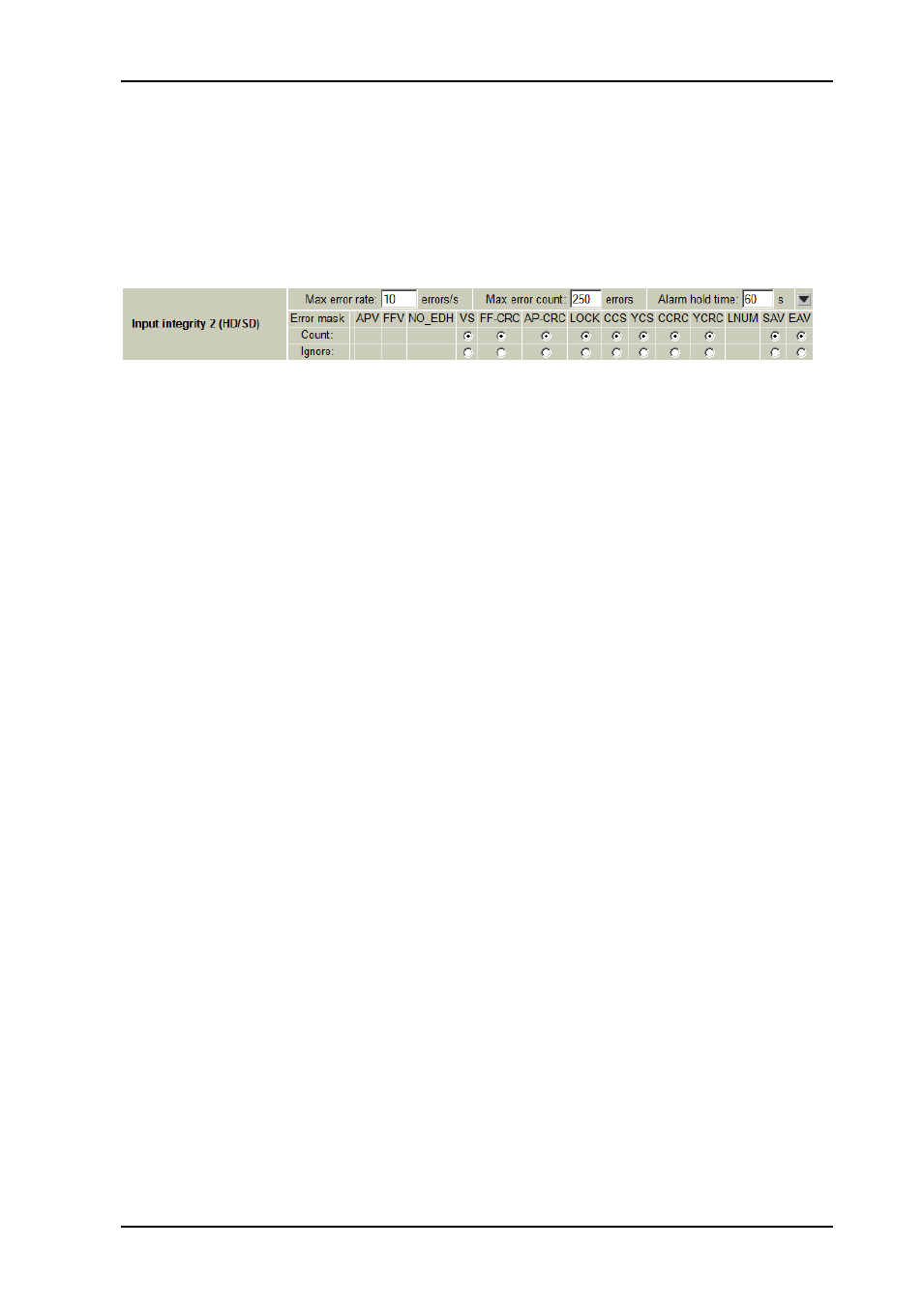

Figure 4: Selection of error bits to be counted or ignored

Eight built-in analyzers

– one for each input or output – will report errors seen in the

previous video frame. The de-mux also has an analyzer for the 10G fiber input. The errors

that can be detected in one or more of the detectors are:

NO_EDH: No EDH flags

VS: Unexpected video format (see ch 3.1.4)

FF-CRC: Full-frame checksum error

AP-CRC: Active picture checksum error

LOCK:

Can’t lock to incoming video standard

CCS / YCS: Checksum error in ancillary data packets, Y or C data space.

CCRC / YCRC: Line checksum error, Y or C (HD only)

LNUM: Unexpected line number sequence (HD only)

SAV: Unexpected Start-of-active-video sequence

EAV: Unexpected End-of-active-video sequence

The operator can select which of the errors are to be counted and which are to be ignored

(masked out). This is done individually for each input or output channel. The error counters

count fields with un-masked errors (for interlaced formats) or frames with un-masked errors

(for progressive formats), not individual errors, of which there can be many in a single field

The maximum error rate generated in a single channel is thus equal to the field rate or

frame rate. Setting the error rate alarm limit in Multicon below the lowest field/frame rate (20

errors/s, for instance) will thus guarantee that any permanent error condition will trigger the

alarm.

If the input to a channel should disappear altogether, an internal counter with a frequency

slightly above 60 Hz will take over. This guarantees that the error rate from the LOCK error

and VS error bits are always at least as high as the error rate generated by the other types

of errors.

The YCS, CCRC and YCRC error bits have no meaning in SD. These are not available for

inputs 7 and 8, which are SD only.

On the de-mux side there are only VS and LOCK error bits available. These error indicators

are actually transported from the mux side; to save power there are no actual error

detectors on the de-mux side, except on the 10G fiber transport stream. If errors are