Frequency information – Altera First-In-First-Out Partitioner User Manual

Page 12

10

Altera Corporation

FIFO Partitioner Megafunction User Guide

Getting Started

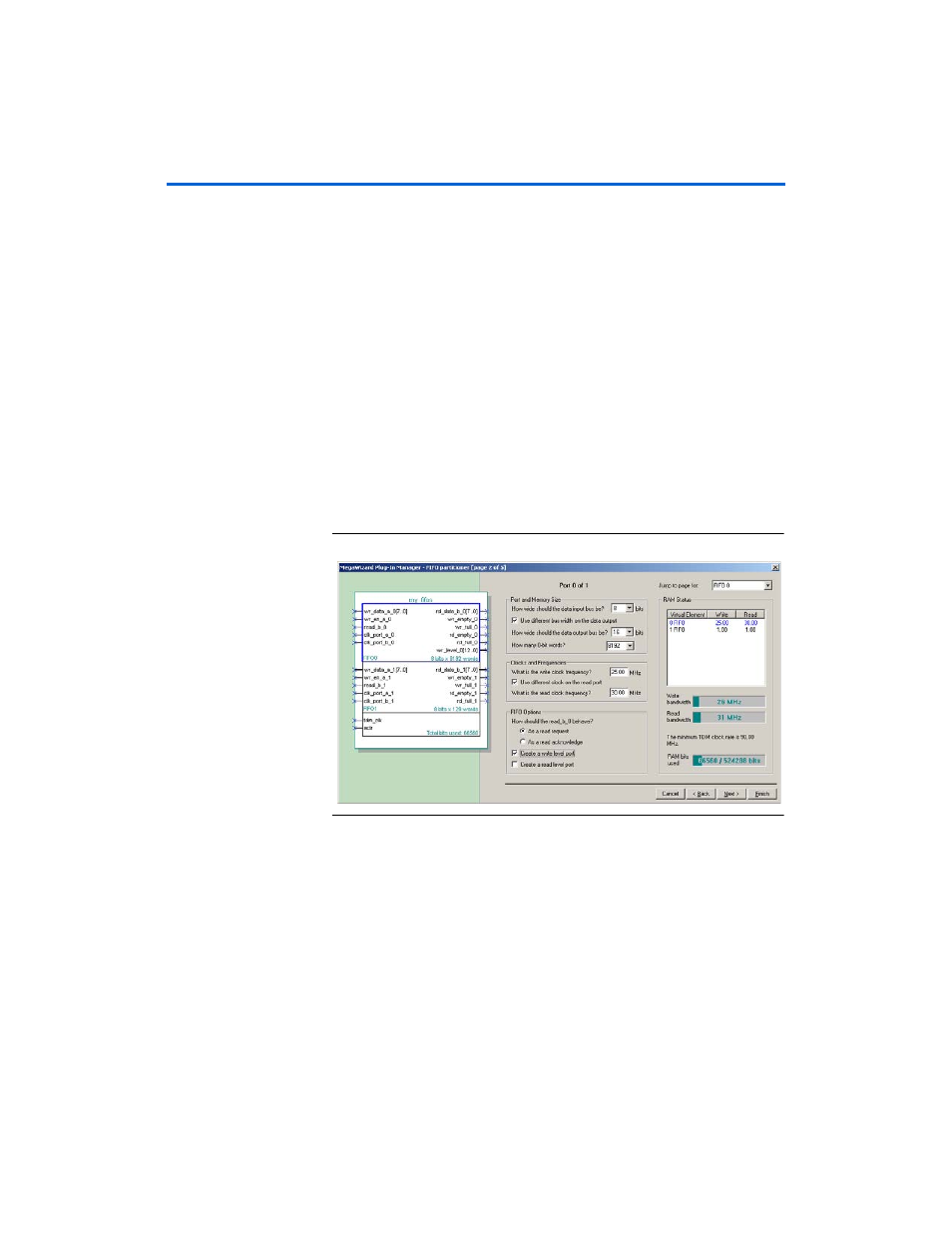

Specify the clock frequencies of the read and write clock ports of each

FIFO. For single-clock FIFOs you need only specify the frequency once,

but the design still has separate clock inputs for the read and write ports.

You should connect them accordingly.

Specify whether the read_b_n signal should behave as a read request or

a read acknowledge input for each FIFO. This determines whether data is

made available on the rd_data_n port before or after read_b_n is

asserted. See the section of this document on FIFO functionality for details

of read_b_n operation.

Specify whether to include read-level and write-level signals for each

FIFO. These signals are optional and indicated to the user how many

words in the FIFO are used. Read-level and write-level signals specify the

current level in words in terms of the respective bus-width. Therefore,

mixed-width FIFOs show different values on the read-level and

write-level output signals.

MegaWizard page for configuring FIFOs.

Figure 4. Configuration Options For FIFOs in the FIFO Partitioner MegaWizard

Frequency Information

After all FIFO configuration information has been specified, the FIFO

Partitioner MegaWizard displays a summary of the frequency

information for all FIFOs. The minimum TDM clock frequency is

displayed and selected by default. You can enter a frequency higher than

the minimum (

).