Port listing for fifo partitioner functions, Table 3 – Altera First-In-First-Out Partitioner User Manual

Page 18

16

Altera Corporation

FIFO Partitioner Megafunction User Guide

Getting Started

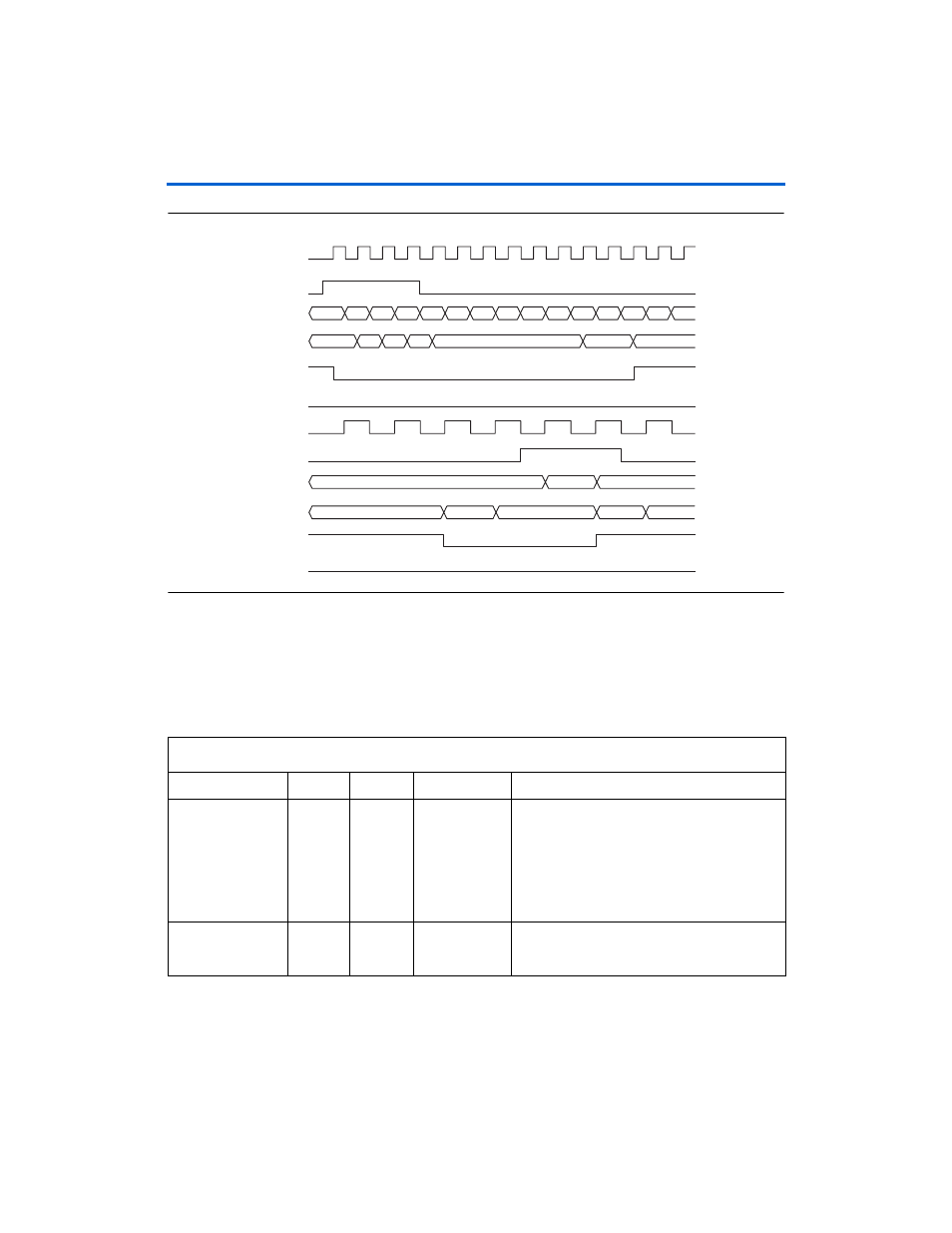

Figure 10. Writing 8-bit words and reading 16-bit words

Port Listing for

FIFO

Partitioner

Functions

summarizes the port listing for FIFO Partitioner Functions.

clk_port_a_3

wr_en_a_3

wr_data_a_3

wr_level_3

wr_empty_3

wr_full_3

clk_port_b_3

read_b_3

rd_data_b_3

rd_level_3

rd_full_3

rd_empty_3

1

0

0000

0

1

1

0

2

0201

0403

2

3

4

2

0

01

02

03

04

05

06

07

08

09

0A

0B

0C

0D

0E

0F

Table 3. FIFO Partitioner Port Listing (Part 1 of 3)

Port Name

Required Direction

Direction

Comments

tdm_clk

Yes

In

Time-domain-

multiplexing

clock port.

The

tdm_clk

requires a minimum frequency of 3

times the fastest FIFO port clock frequency or n

times the fastest FIFO port clock frequency for n

FIFOs. For optimum performance,

tdm_clk

should be run at maximum possible frequency as

specified by hardware constraints and static

timing analysis

aclr

Yes

In

Asynchronous

global reset

Must be asserted for a minimum of 10 ns to

initialize the FIFO Partitioner function. Polarity is

user-defined in the MegaWizard.