Performance of fifo partitioner functions, Figure 2 – Altera First-In-First-Out Partitioner User Manual

Page 9

Altera Corporation

7

Getting Started

FIFO Partitioner Megafunction User Guide

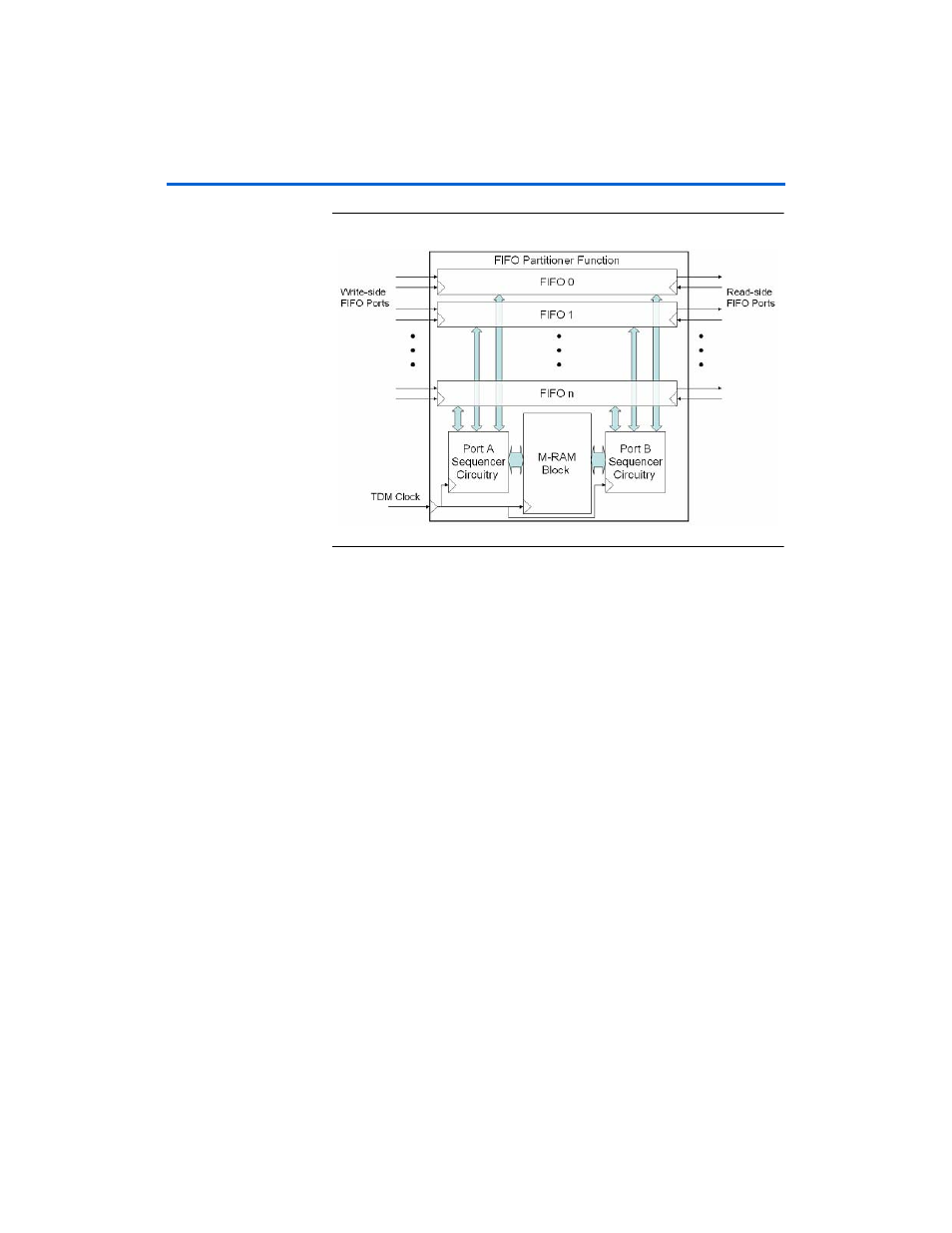

Figure 2. Detailed view of FIFO Partitioner function

When a read or write operation to a FIFO port is initiated, the sequencer

circuitry accesses the physical memory in the fast TDM clock domain. The

sequencer then transfers information back to the clock domain of the FIFO

port completing the memory access. Because of these clock-domain

transfers, performance of the FIFOs is limited by the speed of the

sequencer circuitry and the number of FIFOs in the FIFO Partitioner

function.

Performance of

FIFO

Partitioner

Functions

To ensure that FIFO memory accesses can be serviced, the frequency of the

TDM clock must run at or above Nx the speed of the fastest FIFO port,

where N

3.

(For FIFO Partitioner functions more than 3 FIFOs, N equals

the number of FIFOs.)

1

The upper bound of the TDM clock is the maximum speed of the

memory (approximately 275 MHz for Stratix™ M-RAM blocks).

Depending on how you configure the FIFO Partitioner, the

sequencer circuitry may limit performance.