Fifo functionality, Initializing the fifo, Figure 5 – Altera First-In-First-Out Partitioner User Manual

Page 13

Altera Corporation

11

Getting Started

FIFO Partitioner Megafunction User Guide

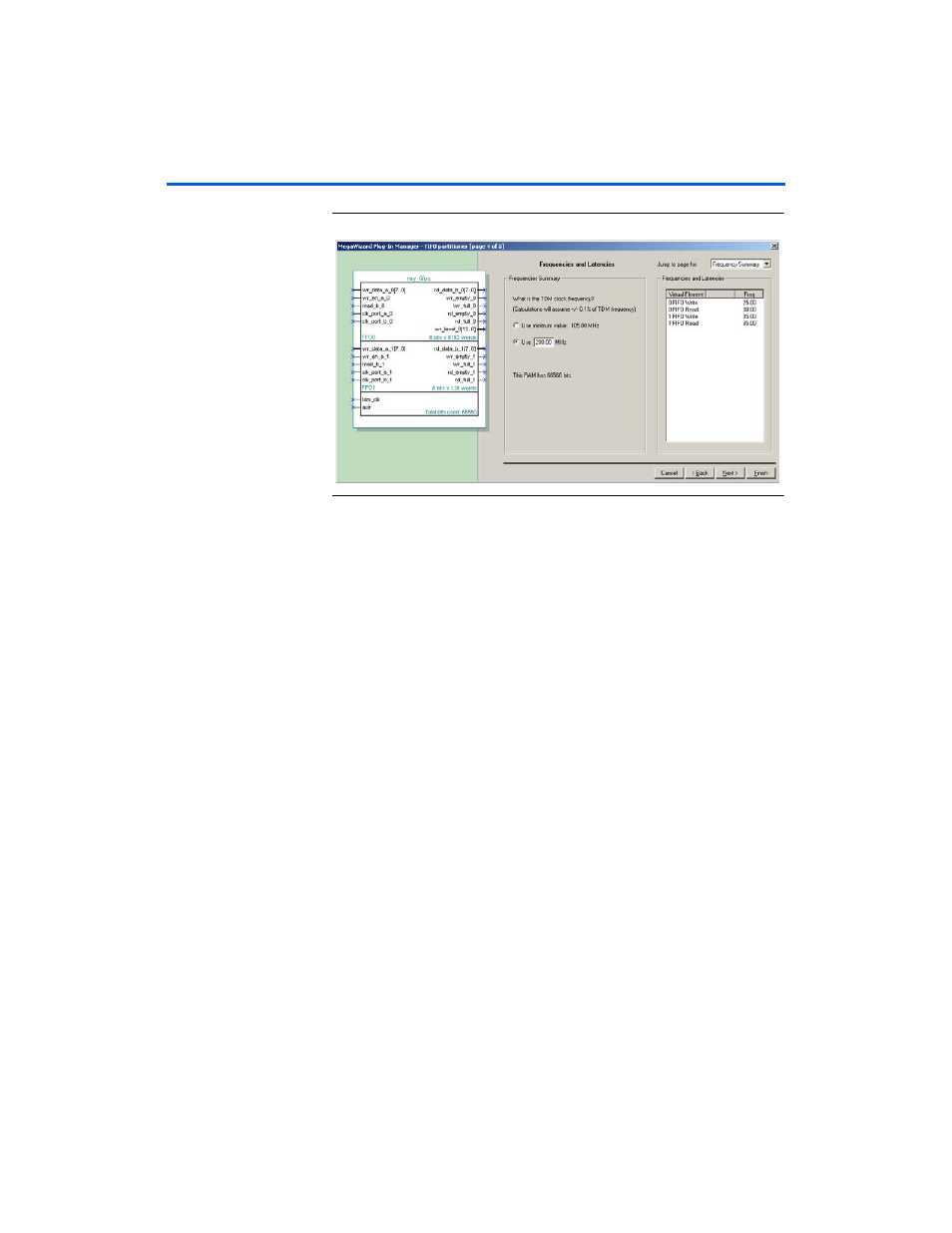

Figure 5. Frequency Information in the FIFO Partitioner MegaWizard

To minimize the effects of internal pipelining on the full and empty flags,

use the highest achievable frequency for the TDM clock. In order to

determine the highest achievable TDM clock performance, run a

preliminary compilation and make sure that the reported f

MAX

for

TDM_clk

is greater than the frequency you have chosen. It is important

that you specify a value for TDM_clk that is accurate to within +/- 0.1%

in order to ensure that the FIFO Partitioner function can operate correctly

and realize the reported latency. Refer to

Empty Flags of FIFOs” on page 14

for a description of how internal

pipelining affects the full and empty flags.

FIFO

Functionality

This section describes the functionality of FIFO's. For more information,

refer to

, FIFO Partitioner Port listing.

Initializing the FIFO

ACLR

must be asserted for a minimum of 10 ns in order to initialize the

FIFO control logic before any read or write operations may be performed.

The port clocks and the TDM_clk must be oscillating at the specified

frequencies in order for the FIFO Partitioner function to operate correctly.

To check what frequency is specified, look at the <functionname>_info.txt

file output by the MegaWizard Plug-In Manager. In order to modify these

frequencies, you must rerun the MegaWizard Plug-In Manager.