Features – Altera First-In-First-Out Partitioner User Manual

Page 8

6

Altera Corporation

FIFO Partitioner Megafunction User Guide

Getting Started

Features

summarizes key features of the FIFO Partitioner.

Time-Domain-

Multiplexing

M-RAM Blocks

For Multiple

FIFOs

Each FIFO operates independently. Each FIFO port has unique clock,

data, control input, and status flag output signals. Total memory

bandwidth is shared, limiting the speed at which each FIFO can be

accessed. Refer to

FIFO ports can be operated in completely asynchronous clock domains.

You must supply frequency information for each FIFO, but you do not

need to specify the phase relationship between clock domains. You must

specify a clock called TDM_clk which is used to time-domain-multiplex

access to the physical memory. A sequencer circuit transfers address, data

and control information between the clock domains of each FIFO and the

TDM clock domain (

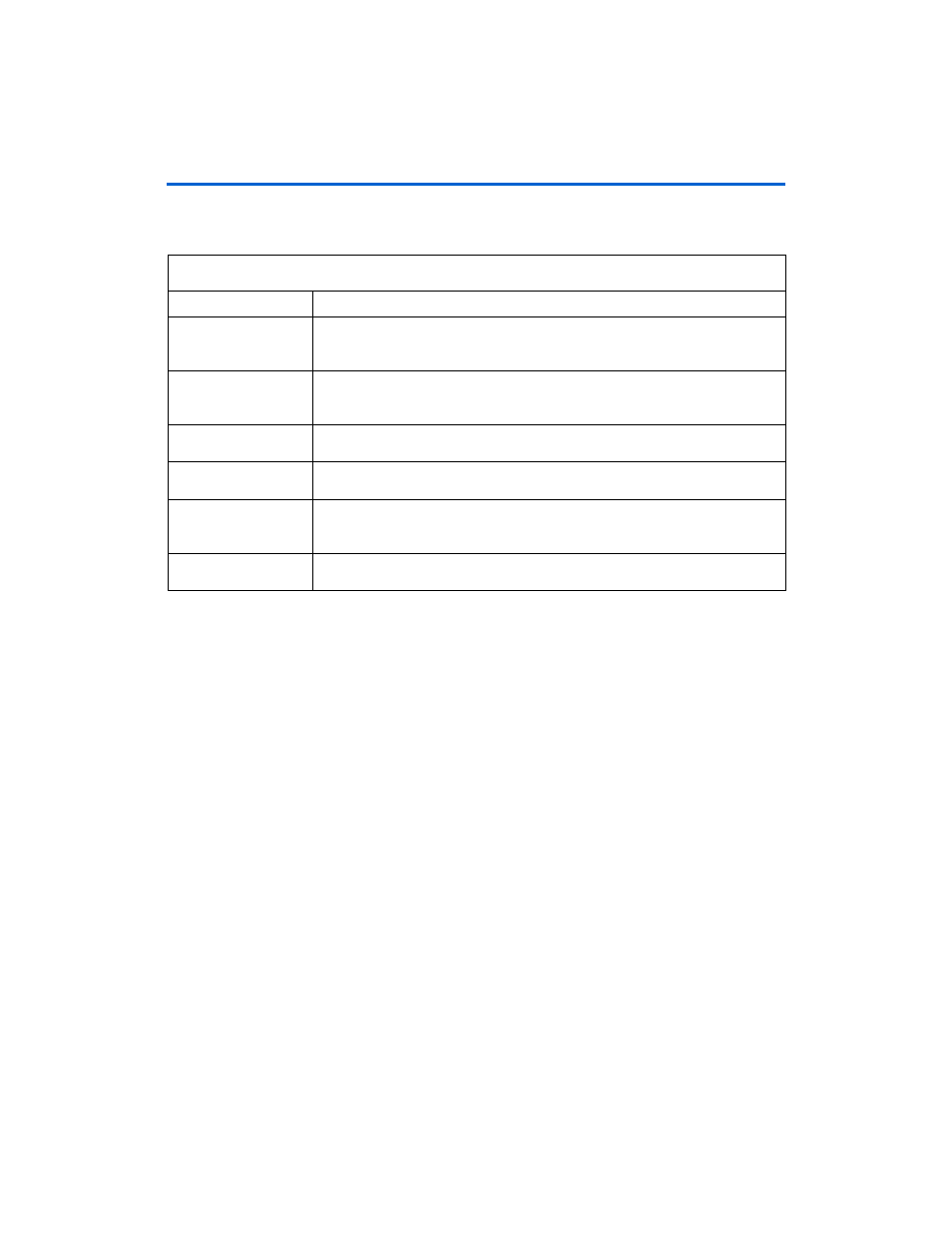

Table 1. FIFO Partitioner Features

Feature

Description

Partition M-RAM Blocks

into Multiple FIFO

functions

Automatically generates all circuitry required to implement multiple, fully independent

FIFOs in a single M-RAM Block. User specifies width, depth, frequency, and behavior

of each FIFO individually, or specifies multiple identical FIFOs.

Dual-clock FIFO

Operation

Read and Write ports of each FIFO can be fully asynchronous to each other. This

makes the FIFO Partitioner ideal for buffering multiple channels of data between clock

domains.

Mixed-width FIFO

Operation

Possible to write data in at one width and read it out at another width. This feature is

ideal for aggregating data for parallel processing tasks.

Read Request Mode

Operation

Data becomes available after

read_b_n

is asserted. This mode is similar to the

Legacy synchronous FIFO mode for LPM_FIFO MegaFunctions.

Read Acknowledge

Mode Operation

Data becomes available before

read_b_n

is asserted. In this mode,

read_b_n

acts as a read acknowledge. This mode is similar to the Show-ahead synchronous

FIFO mode for LPM_FIFO MegaFunctions.

Supports parity bits and

wide data configurations

8, 9, 16, 18, 32, 36, 64, 72, 132, and 144-bit wide configurations supported.

Note to

(1)

Maximum width for mixed-width configurations is 72.