Altera PowerPlay Early Power Estimator User Manual

Page 20

3–4

UG-FPGAPWRCAL-2.0

Altera Corporation

PowerPlay Early Power Estimator User Guide: Stratix, Stratix GX & Cyclone FPGAs

October 2005

PowerPlay Early Power Estimator Input Values

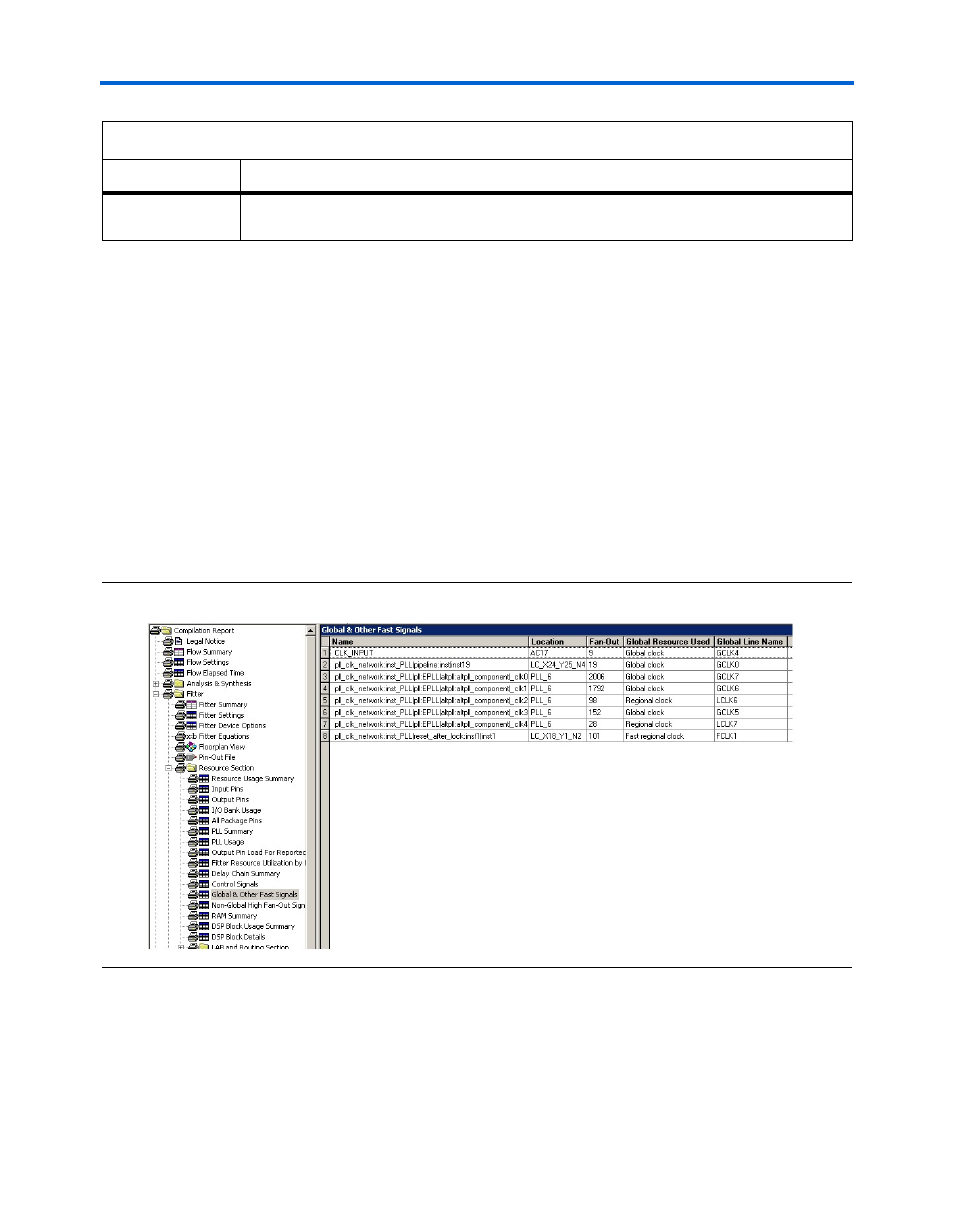

shows a screen shot of the Global & Other Fast Signals report

from the Quartus II software Compilation Report. The report shows

fan-out for each signal that uses a global clock. The Timing Analysis

section of the Compilation Report lists the clock signal frequencies. Enter

the appropriate information from the Compilation Report into the

PowerPlay early power estimator.

shows the Stratix device

PowerPlay early power estimator and the estimated power consumed by

the global clock, regional clock, and fast regional clock networks for this

design.

Figure 3–2. Global & Other Fast Signals Resource Section in Compilation Report

P

I N T

(mW)

This shows the estimated P

I N T

, in mW, based on the f

M A X

and number of flip-flops you

entered. This value is estimated automatically.

Note to

:

(1)

This value is limited by the number of blocks (DSP, M4K, M512, or MRAM) available in the largest device in the

family. You should verify that the number of (DSP, M4K, M512, or MRAM) blocks entered does not exceed the

number of (DSP, M4K, M512, or MRAM) blocks available in your target device because the PowerPlay early power

estimator does not verify this.

Table 3–1. Clock Network Section Information

(Part 2 of 2)

Column Heading

Description