Digital signal processing (dsp) – Altera PowerPlay Early Power Estimator User Manual

Page 33

Altera Corporation

3–15

January 2007

PowerPlay Early Power Estimator For Stratix II, Stratix II GX & HardCopy II

Using the PowerPlay Early Power Estimator

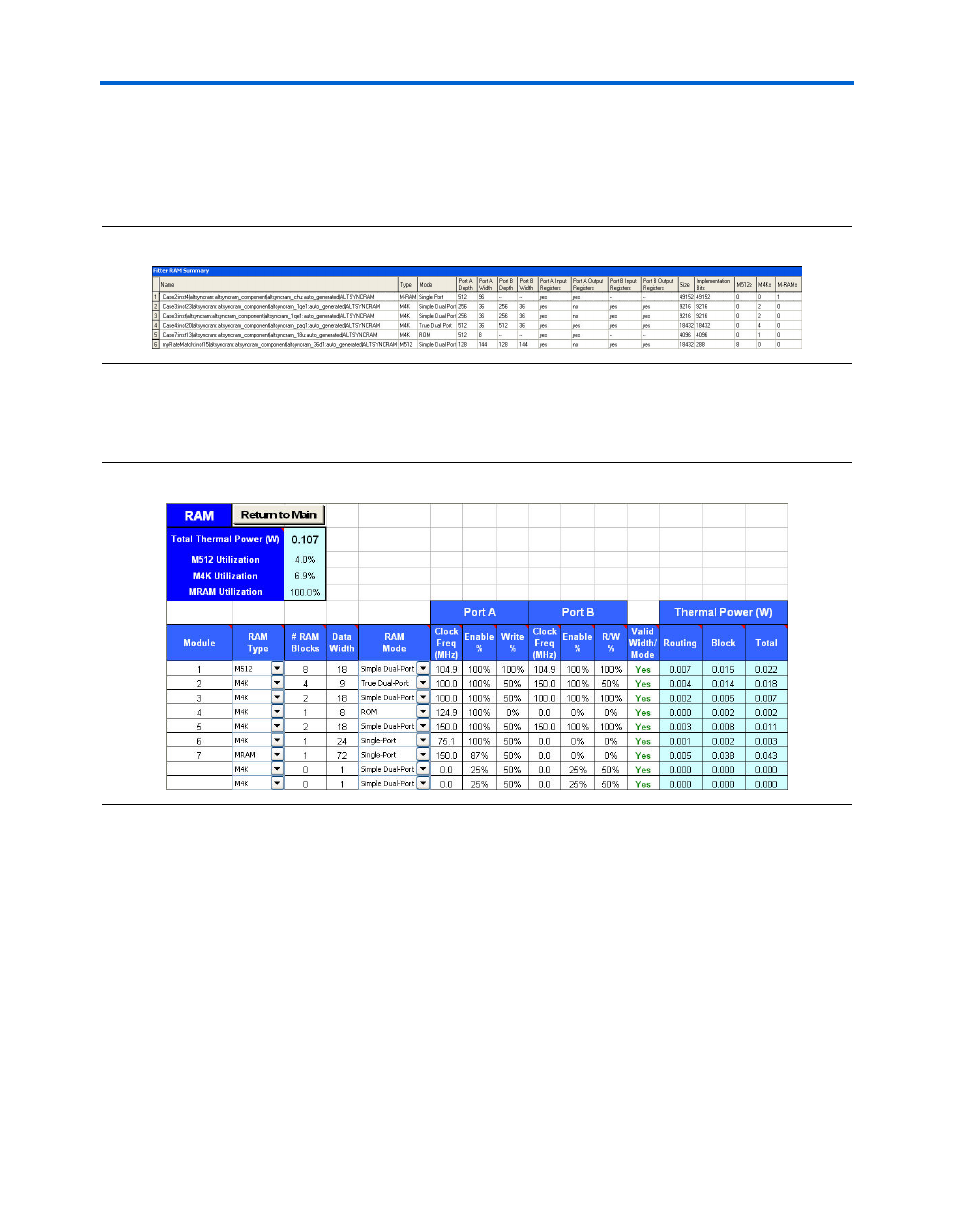

Figure 3–7

shows the RAM Summary in the Quartus II software

Compilation Report for a design targeting the device family. The

Compilation Report provides the RAM type, the RAM mode, and the

data width.

Figure 3–7. RAM Summary in Compilation Report

Figure 3–8

shows the PowerPlay Early Power Estimator spreadsheet and

the estimated power consumed by RAM blocks in this design.

Figure 3–8. RAM Section in the PowerPlay Early Power Estimator

Digital Signal Processing (DSP)

Stratix II and Stratix II GX devices have dedicated DSP blocks that can

implement high-speed parallel processing optimized for DSP

applications. DSP blocks are ideal for implementing DSP applications

that need high data throughput. The Digital Signal Processing (DSP)

section in the PowerPlay Early Power Estimator spreadsheet provides

power information for Stratix II DSP blocks.

1

HardCopy II devices use HCell macros which implement the

supported modes of operation for the Stratix II DSP block.