Phase-locked loops (plls) – Altera PowerPlay Early Power Estimator User Manual

Page 46

3–28

Altera

Corporation

PowerPlay Early Power Estimator For Stratix II, Stratix II GX & HardCopy II

January 2007

PowerPlay Early Power Estimator Inputs

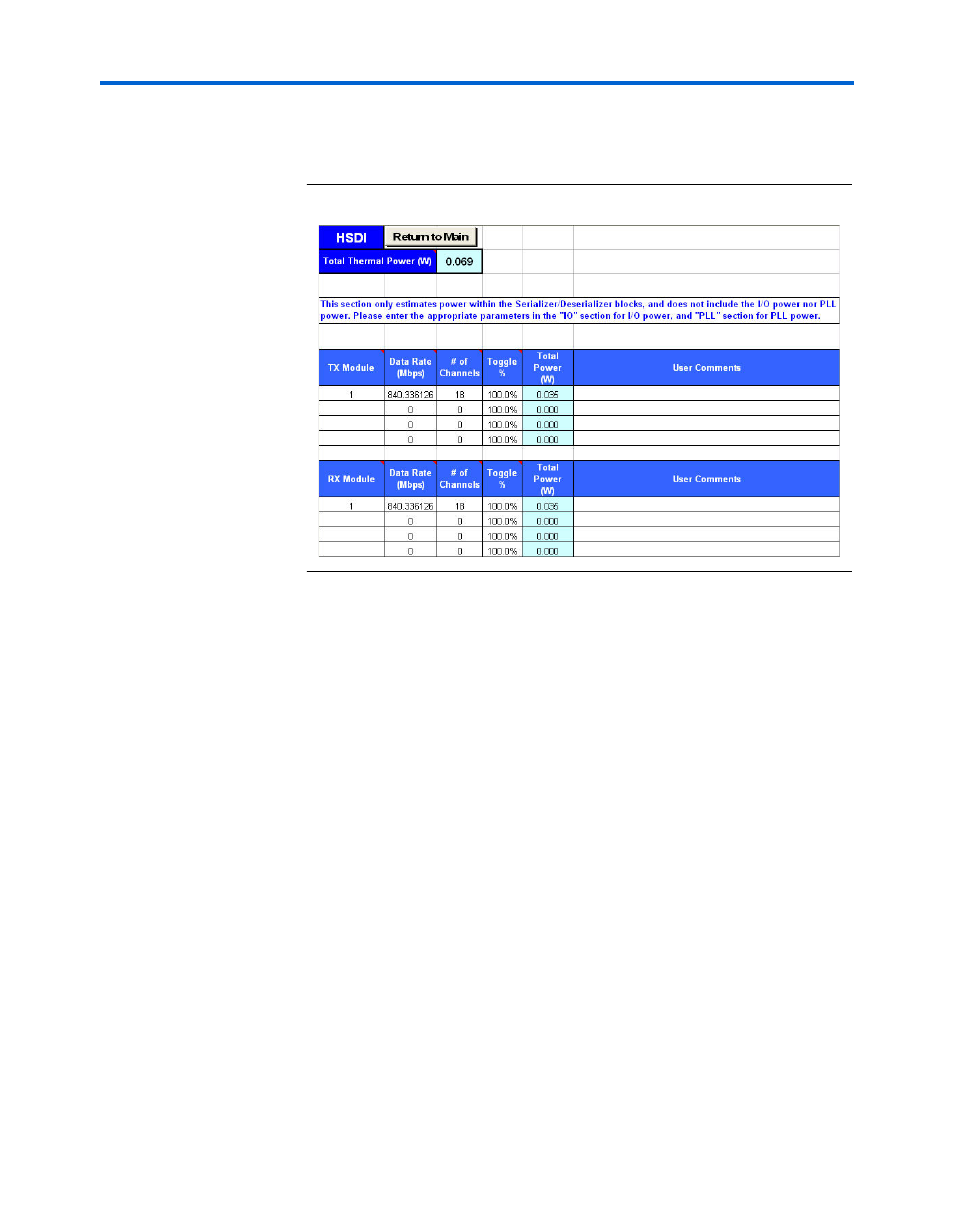

Figure 3–17

shows the PowerPlay Early Power Estimator spreadsheet

and the estimated power consumed by HSDI blocks for this design.

Figure 3–17. HSDI Section in the PowerPlay Early Power Estimator

Phase-Locked Loops (PLLs)

Stratix II, Stratix II GX, and HardCopy II devices feature enhanced and

fast PLLs for general usage. If you are using dedicated transmitters or

receivers and are using an LVDS PLL to implement serialization or

deserialization, specify an LVDS PLL and enter power information in the

PLL

section.

1

When a fast PLL drives LVDS hardware, it is referred to as an

LVDS PLL. LVDS PLLs drive LVDS clock trees and DPA buses at

the VCO frequency (0 to 1040 MHz). If an LVDS PLL drives

LVDS hardware only, enter the appropriate VCO frequency and

specify an output frequency of 0 MHz. If the LVDS PLL also

drives a clock to a pin or to the core, specify that clock frequency

as the output frequency (0 to 550 MHz).