6-1 dram timing setting – Jetway Computer J7F2 User Manual

Page 32

28

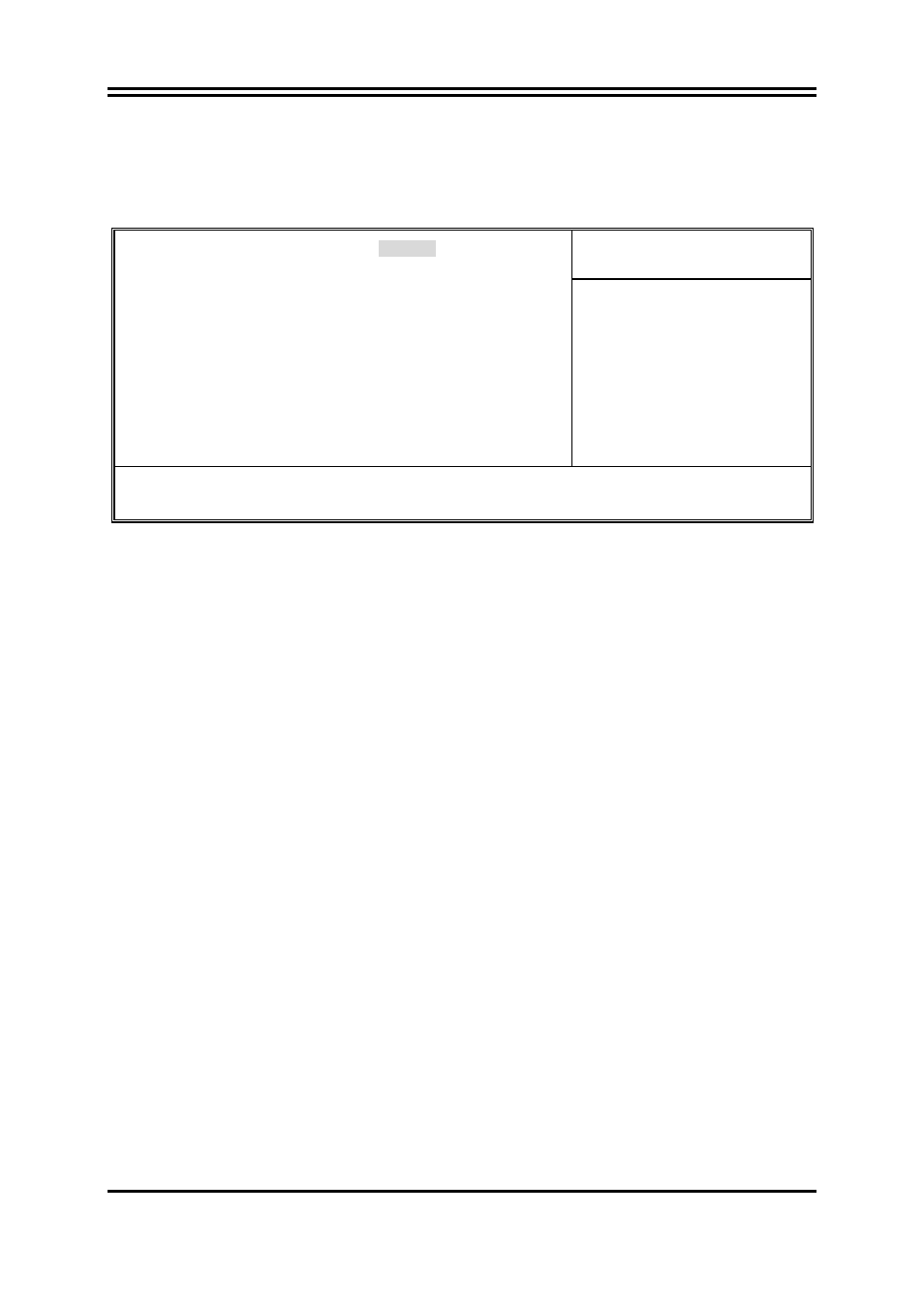

3-6-1 DRAM Timing Setting

Phoenix – AwardBIOS CMOS Setup Utility

DRAM Timing Setting

Item Help

System performance By SPD

RAS Active Time 13T

RAS Precharge Time 3T

RAS to CAS Delay 3T

DRAM CAS Latency 4.0T

Bank Interleave Disabled

Write Recovery Time 5T

DRAM Command Rate 2T

Menu Level >>

↑↓→← Move Enter:Select Item +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Optimized Defaults F7:Standard Defaults

DRAM CAS Latency

When synchronous DRAM is installed, the number of clock cycles of CAS latency depends

on the DRAM timing. The settings are: 2T, 2.5T and 3T.

RAS Precharge Time

If an insufficient number of cycles is allowed for the RAS to accumulate its charge before

DRAM refresh, the refresh may be incomplete and the DRAM may fail to retain date. Fast

gives faster performance; and Slow gives more stable performance. This field applies only

when synchronous DRAM is installed in the system. The settings are: 2T and 3T.

RAS-to-CAS Delay

This field let’s you insert a timing delay between the CAS and RAS strobe signals, used when

DRAM is written to, read from, or refreshed. Fast gives faster performance; and Slow gives

more stable performance. This field applies only when synchronous DRAM is installed in

the system. The settings are: 2T and 3T.