7 integrated peripherals, 6-2 agp timing settings, 6-3 pci timing settings – Jetway Computer J7F2 User Manual

Page 33

29

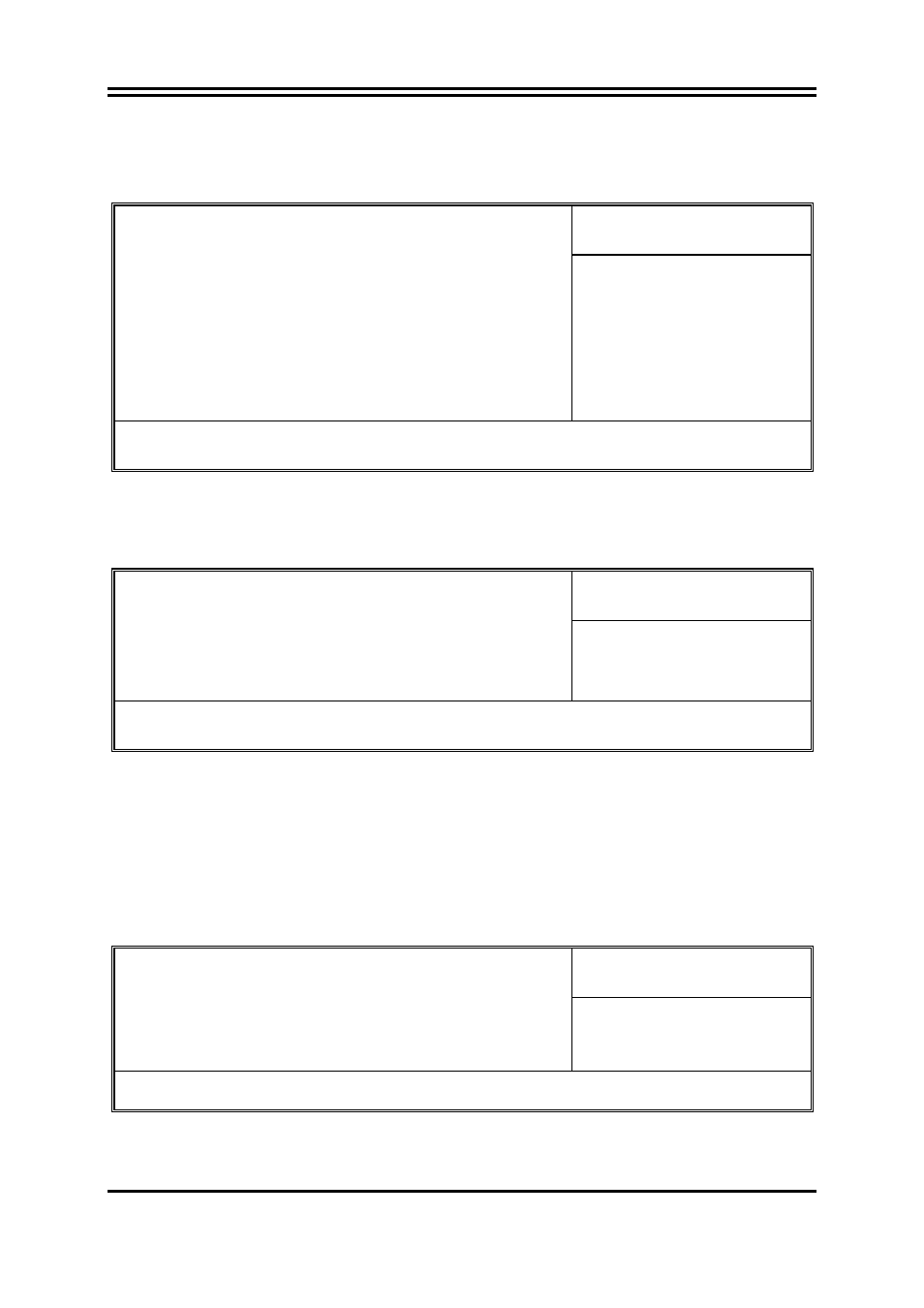

3-6-2 AGP Timing Settings

Phoenix – AwardBIOS CMOS Setup Utility

AGP Timing Settings

Item Help

AGP Aperture Size 128MB

AGP Transfer Mode 8X

AGP Driving Control Auto

AGP Fast Write Disabled

AGP Master 1 WS Write Disabled

AGP Master 1 WS Read Disabled

CPU to AGP Post Write Enabled

AGP Delay Transaction Enabled

AGP3.0 Calibration Cycle Disabled

VGA Share Memory Size 64MB

Direct Frame Buffer Disabled

Select Display Device CRT

Menu Level >>

↑↓→← Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Optimized Defaults F7:Standard Defaults

3-6-3 PCI Timing Settings

Phoenix – AwardBIOS CMOS Setup Utility

PCI Timing Settings

Item Help

PCI Master 1 WS Write Disabled

PCI Master 1 WS Read Disabled

CPU to PCI Post Write Enabled

PCI Delay Transaction Enabled

VLink Mode Selection BY Auto

VLink 8X Support Enabled

DRDY-Timing Slowest

Menu Level >>

↑↓→← Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Optimized Defaults F7:Standard Defaults

PCI Delay Transaction

The chipset has an embedded 32-bit posted write buffer to support delay transactions cycles.

Select Enabled to support compliance with PCI specification version 2.1. The settings are:

Enabled and Disabled.

3-7

Integrated

Peripherals

Phoenix – AwardBIOS CMOS Setup Utility

Integrated Peripherals

Item Help

OnChip IDE Function Press Enter

OnChip Device Function Press Enter

OnChip SIO Function Press Enter

Init Display First PCI Slot

Menu Level >

↑↓→← Move Enter:Select Item +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Optimized Defaults F7:Standard Defaults