Block diagram - architecture, Figure 1 - block diagram, Xilinx fpga – Sundance SMT370v2 User Manual

Page 7: Option to the board

Version 2.0

Page 7 of 46

SMT370v2/v3 User Manual

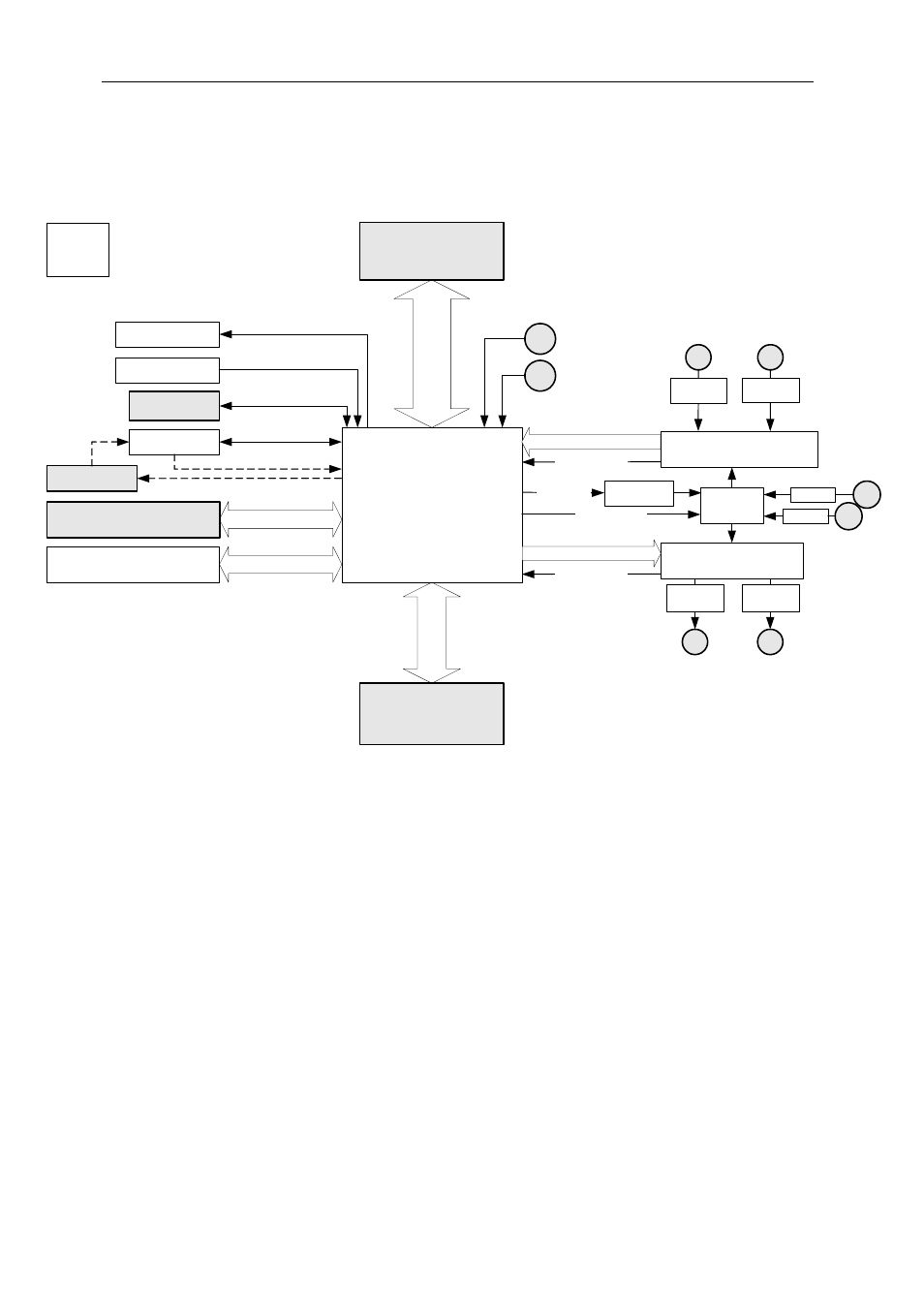

Block Diagram - Architecture.

The following diagram shows the architecture of the SMT370.

B

o

ar

d Re

se

t

2x

Com

m

-P

o

rt/S

DL

24

I

/O

p

in

s

68 I/O pins; 32-bit data

Xilinx FPGA

Virtex-II, FG456

XC2V1000-6

324 I/O Pins

1.5V Core

3.3V I/O

One bank of 1Mx32 bits of

NtSRAM - 166 MHz

J2 Bottom Primary TIM

Connector

J1 Top Primary TIM

Connector

2x CommPorts/SDLs 0 & 3

#1

120 I/O pins

AC or DC

coupling*

2xAD6645 ADCs

14-bit @ 105MSPS

52-pin LQFP

30 I/O pins; 28-bit data; ctl

1x AD9777 DAC

16-bit @ 400MSPS

80-pin TQFP

44 I/O pins; 16-bit data; ctl

#4

#3

RF

transformer

#2

Clock feedback

Trig

1

Trig

2

6-pin JTAG

header

On-board Oscillator

50 MHz

4 LEDs or

4 LVTTL I/O pins

FPGA PROM

XC18V04

Clock

Multiplexer

Clock

parameters

3 Power

supply

LEDs

‘FPGA configured’

LED

Clock feedback

Clk

1

Filter

Filter

2xClock

synthesizers

Clk

2

Clock selection

2 Sundance High-speed

Bus connector: 2 x 60 bits

AC or DC

coupling*

RF

transformer

JTAG chain

* Option to the board

Figure 1 - Block Diagram.

Connections to the outside world are greyed out.

Main parts of the board are described in the next part of this document.