Verilink DIU 2130 (880-503297-001) Product Manual User Manual

Page 84

DIU/DIM Details

7-4

Verilink

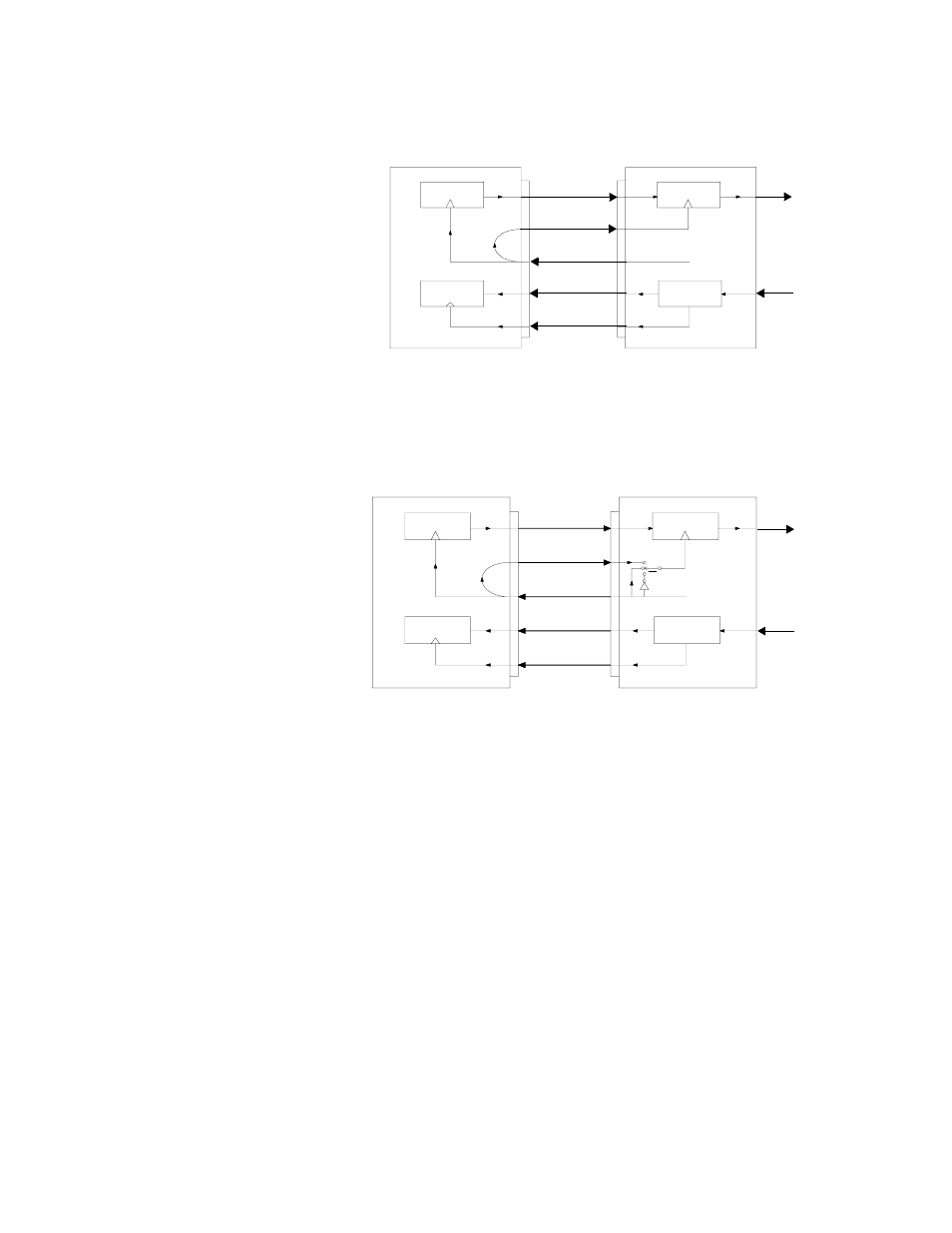

Figure 7-6 Send Timing (ST)

Since TT must be locked to ST, most DTE manufacturers turn ST

around on TT, and TT is usually an exact duplicate of ST. (Figure

7-7)

Figure 7-7 Interface Timing Options

Therefore, the DIU can be set to clock in SD using ST instead of TT.

Consequently, some DTE manufacturers do not implement the TT

signal. If the cable between the DIU and DTE is long enough, the

DIU may require setting the clock for inverted ST rather than ST;

this allows for a slight phase shift.

For the DCE-DTE interface to function properly, the data signals

must be synchronized with the associated clock signals. Therefore,

the following signals (if implemented) must be synchronized:

•

RD with RT

•

TT with ST with SD

In the T1 transmit direction, SD and TT (if implemented) must both

be synchronized with ST. The ST is derived from the T1 transmit

clock, and is generated using one of one the following timing

methods (Figure 7-8):

•

Network Loop Timing (T1 Bit Stream)

•

Internal Timing (Master Clock)

•

External Timing (Station Clock)

Customer

Equipment

(DTE)

DSU

(DCE)

T1 XMT

T1 RCV

Clock

Recovery

Receive

Input Buffer

SD

RD

TT

RT

Buffer

ST

XMT Buffer

Customer

Equipment

(DTE)

DSU

(DCE)

T1 XMT

T1 RCV

Clock

Recovery

Receive

Input Buffer

SD

RD

TT

RT

Buffer

ST

XMT Buffer

TT

ST

ST