Jtag pin sharing behavior – Altera MAX 10 FPGA User Manual

Page 30

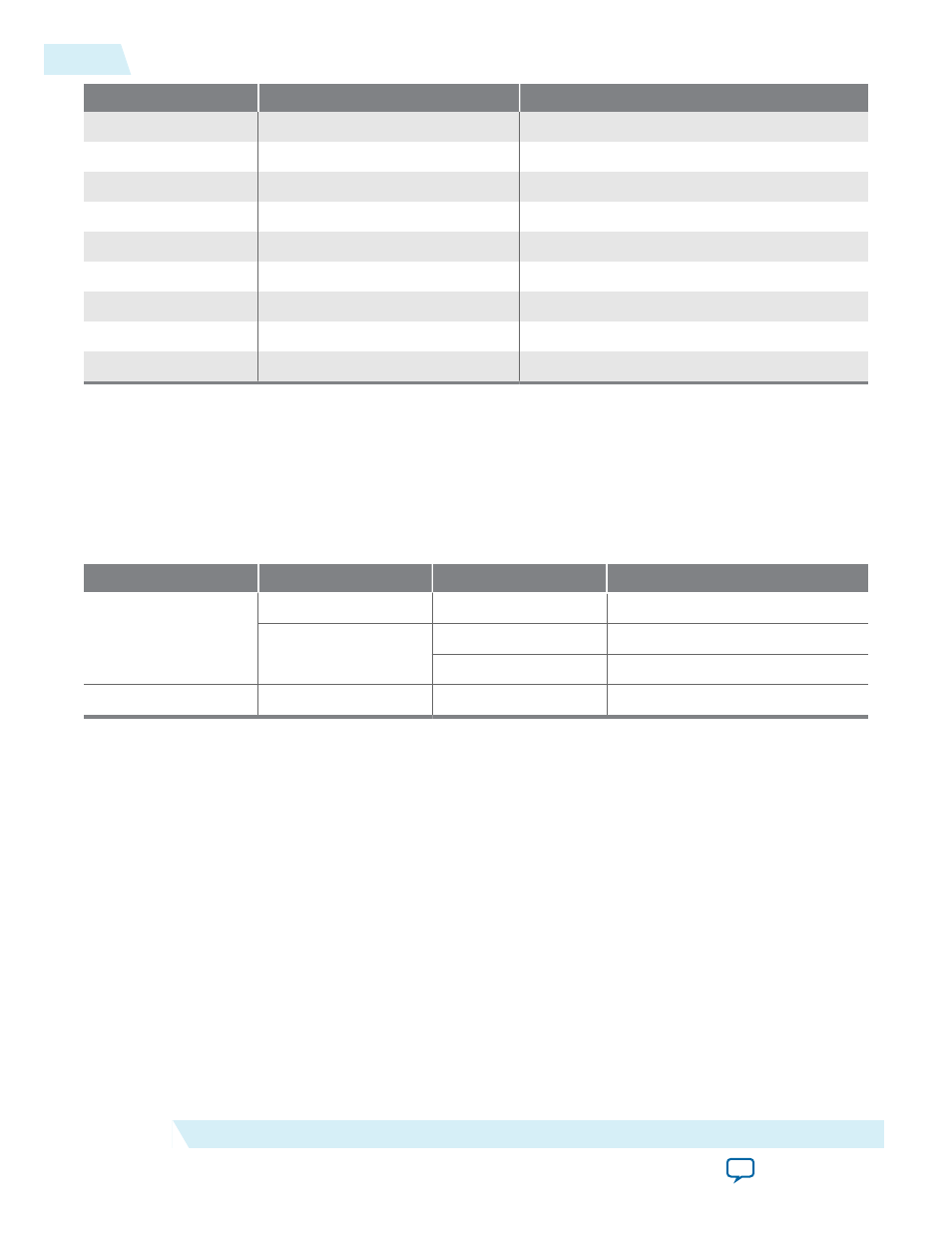

Configuration Pin

Input/Output

Configuration Scheme

DEV_OE

Input only

Optional, JTAG and internal configurations

CONF_DONE

Bidirectional, open-drain

JTAG and internal configurations

nCONFIG

Input only

JTAG and internal configurations

nSTATUS

Bidirectional, open-drain

JTAG and internal configurations

JTAGEN

Input only

Optional, JTAG configuration

TCK

Input only

JTAG configuration

TDO

Output only

JTAG configuration

TMS

Input only

JTAG configuration

TDI

Input only

JTAG configuration

Related Information

•

Guidelines: Dual-Purpose Configuration Pin

on page 3-1

•

on page 3-2

JTAG Pin Sharing Behavior

Table 2-23: JTAG Pin Sharing Behavior for MAX 10 Devices

Configuration Stage

JTAG Pin Sharing

JTAGEN

Pin

JTAG Pins (

TDO

,

TDI

,

TCK

,

TMS

)

User mode

Disabled

User I/O pin

Dedicated JTAG pins.

Enabled

Driven low

User I/O pins.

Driven high

Dedicated JTAG pins.

Configuration

Don’t Care

Not used

Dedicated JTAG pins.

2-26

JTAG Pin Sharing Behavior

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Schemes and Features