Fir ii ip core features, Dsp ip core device family support, Fir ii ip core features -2 – Altera FIR Compiler II MegaCore Function User Manual

Page 5: Dsp ip core device family support -2

• Avalon

®

Streaming (Avalon-ST) interfaces

• DSP Builder ready

• Testbenches to verify the IP core

• IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators

FIR II IP Core Features

• Exploiting maximal designs efficiency through hardware optimizations such as:

• Interpolation

• Decimation

• Symmetry

• Decimation half-band

• Time sharing

• Easy system integration using Avalon Streaming (Avalon-ST) interfaces.

• Memory and multiplier trade-offs to balance the implementation between logic elements (LEs) and

memory blocks (M512, M4K, M9K, M10K, M20K, or M144K).

• Support for run-time coefficient reloading capability and multiple coefficient banks.

• User-selectable output precision via truncation, saturation, and rounding.

DSP IP Core Device Family Support

Altera offers the following device support levels for Altera IP cores:

• Preliminary support—Altera verifies the IP core with preliminary timing models for this device family.

The IP core meets all functional requirements, but might still be undergoing timing analysis for the

device family. You can use it in production designs with caution.

• Final support—Altera verifies the IP core with final timing models for this device family. The IP core

meets all functional and timing requirements for the device family. You can use it in production

designs.

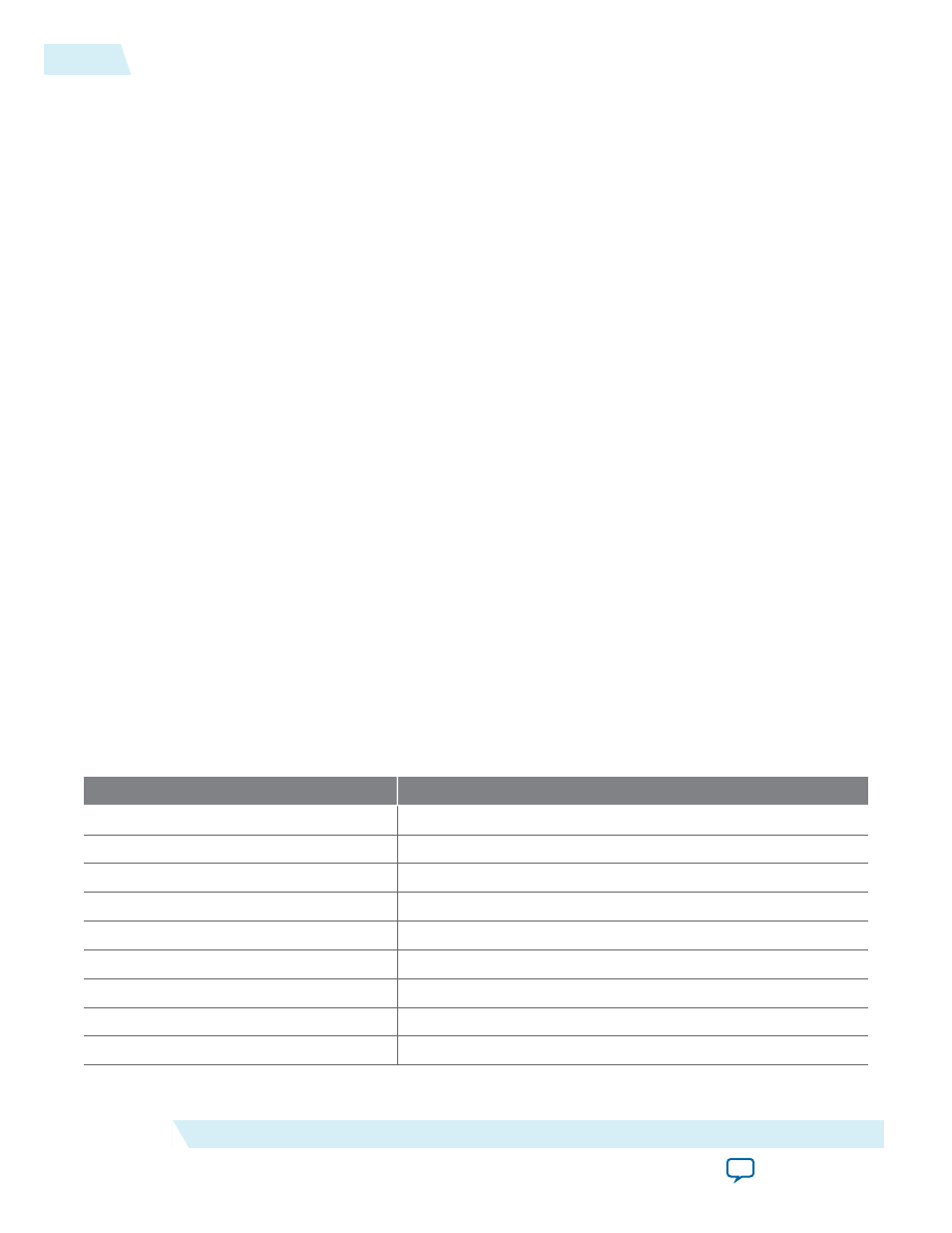

Table 1-1: DSP IP Core Device Family Support

Device Family

Support

Arria

®

II GX

Final

Arria II GZ

Final

Arria V

Final

Arria 10

Final

Cyclone

®

IV

Final

Cyclone V

Final

MAX

®

10 FPGA

Final

Stratix

®

IV GT

Final

Stratix IV GX/E

Final

1-2

FIR II IP Core Features

UG-01072

2014.12.15

Altera Corporation

About the FIR II IP Core