Fir ii ip core coefficient reloading, Fir ii ip core coefficient reloading -21, Loading coefficients from a file on page 3-3 – Altera FIR Compiler II MegaCore Function User Manual

Page 54: Signal before reloading

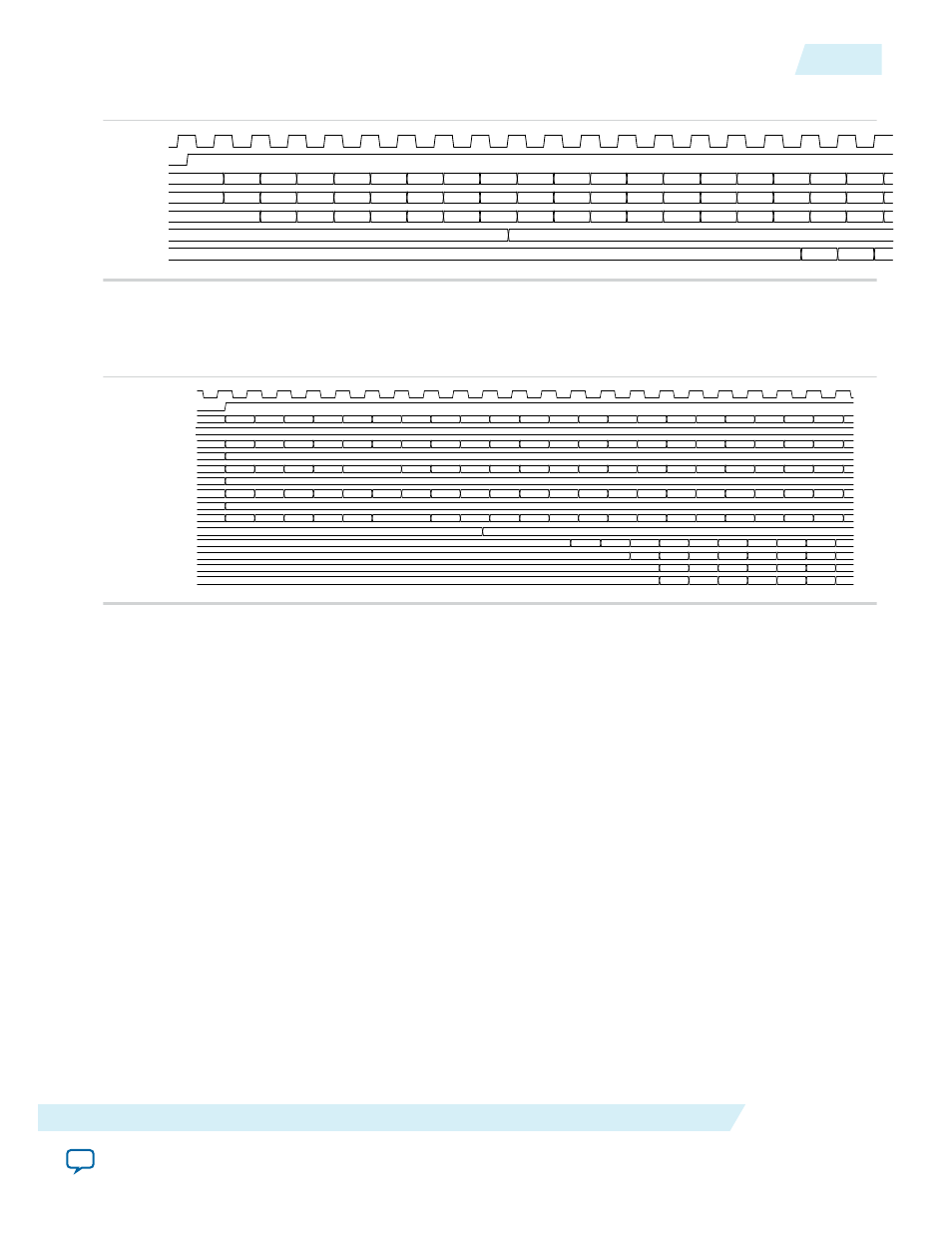

Figure 4-28: Timing Diagram of a Single-Channel Filter with 4 Coefficient Banks

clk

ast_sink_valid

ast_sink_data[9:0]

bankin_0[1:0]

xin_0[7:0]

xout_v[0]

xout_0[21:0]

256

-478 -179

118

408

-259 -159 135

427

-433 -79

122

481

-396

-15

48

429

-262

1

2

3

0

1

2

3

0

1

2

3

0

1

2

3

0

1

2

34

77

118

-104 -3

97

-121 -85

79

-79

122

-31

116

-15

48

-83

-6

411

279

0

0

0

0

0

1

Figure 4-29: Timing Diagram of a Four-Channel Filter with 4 Coefficient BanksEach channel has a

separate corresponding coefficient set. The bank inputs for different channels are driven with their

channel number respectively throughout the filter operation

clk

ast_sink_valid

ast_sink_data[39:0]

bankin_0[1:0]

xin_0[7:0]

bankin_1[1:0]

xin_1[7:0]

bankin_2[1:0]

xin_2[7:0]

bankin_3[1:0]

xin_3[7:0]

xout_v[0]

xout_0[21:0]

xout_1[21:0]

xout_2[21:0]

xout_3[21:0]

-15...

-17... -55...

-20... -23... -30...

-30... -16... -21... -24...

-14... -14... -12... -41... -25...

-17... -26...

-25... -20...

-80... -13...

-41

24

29

-65

-109

34

-15

18

77

-82

25

127

-42

-18

-96

-4

79

27

88

-91

-84

52

67

71

-78

-82

-22

55

115

120

-51

-28

-124

-81

-16

67

-104

47

-27

50

33

46

-37

22

29

-102

-125

-12

-10

-21

-48

56

15

32

31

-23

125

-105

57

-17

12

93

109

96

-52

67

33

-29

99

57

29

125

122

-114

-39

21

88

4

22

61

-8

-126

-82

-75

7

-12

-261

-162

16

231

550 1....

104

186

157

-412

-804

-464

1040 2...

46

-83

-33

219

-148

-402 5...

109

-13

-148

337

-278

-441 8...

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

2

3

Related Information

Loading Coefficients from a File

on page 3-3

FIR II IP Core Coefficient Reloading

You access the internal data coefficients via a memory-mapped interface that consists of the input

address, write data, write enable, read data, and read valid signals. The Avalon Memory-Mapped (Avalon-

MM) interfaces operate as read and write interfaces on the master and slave components in a memory-

mapped system. The memory-mapped system components include microprocessors, memories, UARTs,

timers, and a system interconnect fabric that connects the master and slave interfaces. The Avalon-MM

interfaces describe a wide variety of components, from an SRAM that supports simple, fixed-cycle read

and write transfers to a complex, pipelined interface capable of burst transfers. In Read mode, the IP core

reads the memory-mapped coefficients over a specified address range. In Write mode, the IP core writes

the coefficients over a specified address range. In Read/Write mode, you can read or write the coefficients

over a specified address range. You can use a separate bus clock for this interface. When you do not

enable coefficient reloading option, the processor cannot access the specified address range, and the IP

core does not read or write the coefficient data.

Coefficient reloading starts anytime during the filter run time. However, you must reload the coefficients

only after you obtain all the desired output data to avoid unpredictable results. If you use multiple

coefficient banks, you can reload coefficient banks that are not used and switch over to the new coefficient

set when coefficient reloading is complete. You must toggle the

coeff_in_areset

signal before reloading

UG-01072

2014.12.15

FIR II IP Core Coefficient Reloading

4-21

FIR II IP Core Functional Description

Altera Corporation