Signal. when the, Signal is high, the read data is available on – Altera FIR Compiler II MegaCore Function User Manual

Page 55

the coefficient with new data. The new coefficient data is read out after coefficient reloading to verify

whether the coefficient reloading process is successful. When the coefficient reloading ends by deasserting

the

coeff_in_we

, the input data is inserted immediately to the filter that is reloaded with the new

coefficients.

The symmetrical or anti-symmetrical filters have fewer genuine coefficients, use fewer registers, and

require fewer writes to reload the coefficients. For example, only write the first 19 addresses for a 37-tap

symmetrical filter. When you write to all 37 addresses, the IP core ignores last 18 addresses because they

are not part of the address space of the filter. Similarly, reading coefficient data from the last 18 addresses

is also ignored.

When the FIR uses multiple coefficient banks, it arranges the addresses of all the coefficients in consecu‐

tive order according to the bank number.

The following example shows a 37-tap symmetrical/anti-symmetrical filter with four coefficient banks:

• Address 0–18: Bank 0

• Address 19–37: Bank 1

• Address 38–56: Bank 2

• Address 57–75: Bank 3

The following example shows a 37-tap non-symmetrical/anti-symmetrical filter with 2 coefficient banks:

• Address 0–36: Bank 0

• Address 37–73: Bank 1

If the coefficient bit width parameter is equal to or less than 16 bits, the width of the write data is fixed at

16 bits. If the coefficient bit width parameter is more than 16 bits, the width of the write data is fixed at 32

bits.

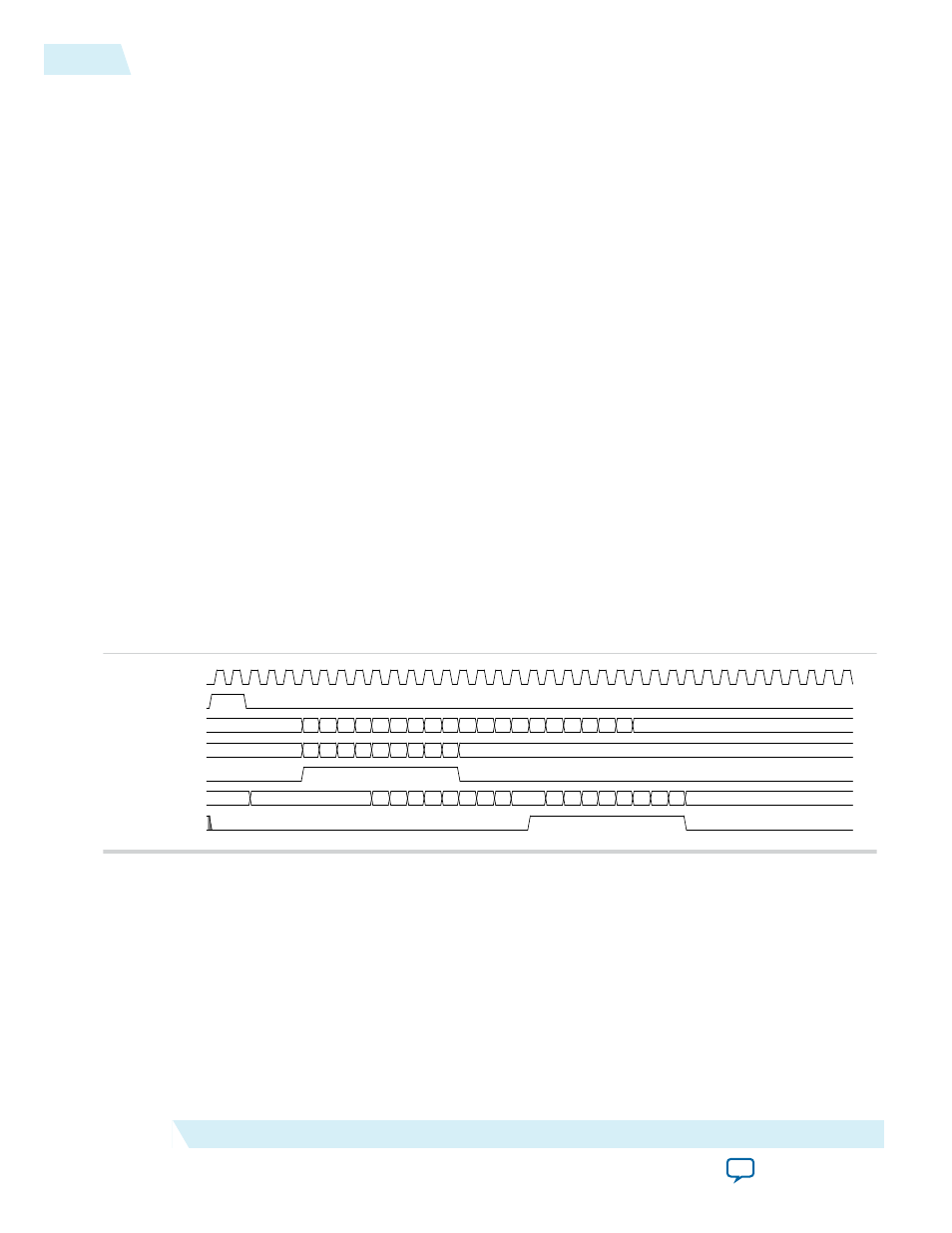

Figure 4-30: Timing Diagram of Coefficient Reloading in Read/Write modeWith nine coefficients.

clk

coeff_in_areset

coeff_in_address[11:0]

coeff_in_data[15:0]

coeff_in_we[0]

coeff_out_data[15:0]

coeff_out_valid[0]

-1

0

1

2

3 4

5

6

7

8

0

1

2

3

4

5

6

7

8

-1

0

-26

45

-1

45 -50 7 -121 -32 49 -1 108 124 -1

-25 13 80 127 80 0 -26 0

-50 7 -1 -32 49 -1 108 124 45

The IP core performs a write cycle of 9 clock cycles to reload the whole coefficient data set. To complete

the write cycle, assert the

coeff_in_we

signal, and provide the address (from base address to the max

address) together with the new coefficient data. Then, load the new coefficient data into the memory

corresponding to the address of the coefficient. The IP core reads new coefficient data during the write

cycle when you deassert the

coeff_in_we

signal. When the

coeff_out_valid

signal is high, the read data

is available on

coeff_out_data

.

4-22

FIR II IP Core Coefficient Reloading

UG-01072

2014.12.15

Altera Corporation

FIR II IP Core Functional Description