Altera RapidIO II MegaCore Function User Manual

Page 111

Chapter 4: Functional Description

4–69

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

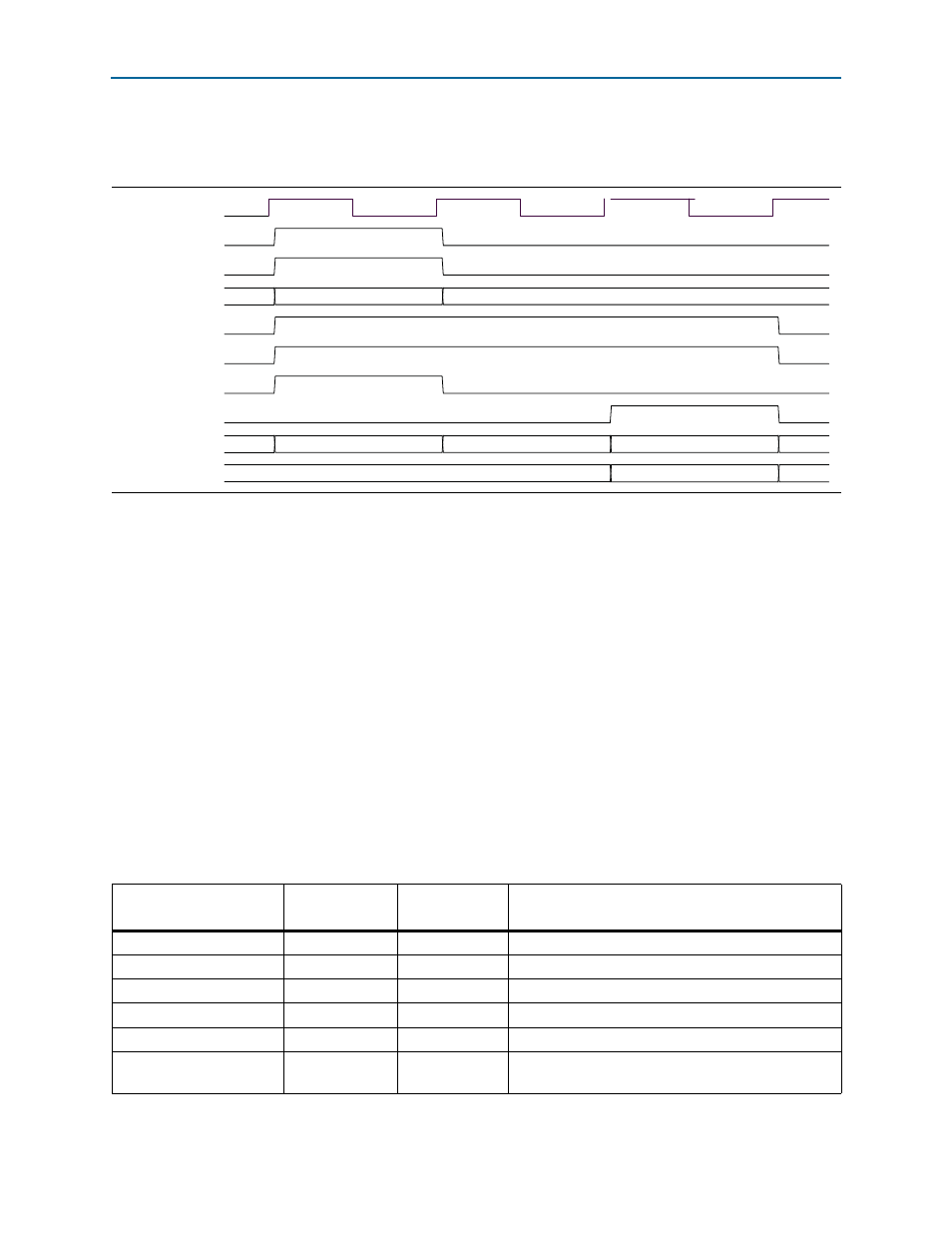

Figure 4–26

shows the behavior of the signals on the Avalon-ST pass-through

interface for this example transaction.

In the first clock cycle of the example, user logic asserts gen_rx_hd_ready and

gen_rx_pd_ready

, and the IP core asserts gen_rx_hd_valid and gen_rx_pd_valid,

indicating it is providing valid data on gen_rx_hd_data and gen_rx_pd_data,

respectively. The assertion of both the ready signal and the valid signal on each of the

header and payload-data Avalon-ST interfaces makes the current cycle an Avalon-ST

ready cycle for both header and data.

The IP core asserts gen_rx_pd_startofpacket to indicate the current cycle is the first

valid data cycle of the packet. In this clock cycle, the IP core also makes the header

and the first 128 bits of payload data available on gen_rx_hd_data and

gen_rx_pd_data

, respectively. The 40-byte payload requires 3 clock cycles. In the third

clock cycle of data transfer, the IP core asserts gen_rx_pd_endofpacket to indicate this

is the final clock cycle of data transfer, and specifies in gen_rx_pd_empty that in the

current clock cycle, the four least significant two-byte segments (the least significant

eight bytes) of gen_rx_pd_data are not valid. Following the clock cycles in which valid

data is available on gen_rx_pd_data, the IP core deasserts gen_rx_pd_valid.

Table 4–35

lists the header fields in this example.

Figure 4–26. Avalon-ST Pass-Through Interface SWRITE Receive Example

clk

gen_rx_hd_ready

gen_rx_hd_valid

0A0C600DD00AA00000AABBCC80000

FFFEFDFCFBFAF9F8F7F6F5F4F3F2F1F0

EFEEEDECEBEAE9E8E7E6E5E4E3E2E1E0

4

gen_rx_hd_data[114:0]

gen_rx_pd_valid

gen_rx_pd_ready

gen_rx_pd_startofpacket

gen_rx_pd_endofpacket

gen_rx_pd_data[127:0]

gen_rx_pd_empty[2:0]

Table 4–45. SWRITE Request Receive Example: RapidIO Header Fields in gen_rx_hd_data Bus (Part 1 of 2)

Field

gen_rx_hd_data

Bits

Value

Comment

pd_size[8:0]

[114:106]

9’h028

Payload data size is 0x28 (decimal 40).

VC

[105]

0

The RapidIO II IP core supports only VC0.

CRF

[104]

0

prio[1:0]

[103:102]

2’b11

tt[1:0]

[101:100]

2’b00

Indicates 8-bit device IDs.

ftype[3:0]

[99:96]

4’b0110

The value of 6 indicates a Streaming-Write Class

packet.