Altera RapidIO II MegaCore Function User Manual

Page 209

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

B. Differences Between RapidIO II

MegaCore Function v12.1 and RapidIO

MegaCore Function v12.1

This appendix lists the basic differences between the Altera RapidIO MegaCore

function, a product available through many previous Altera software releases, and the

new RapidIO II MegaCore function in the 12.1 software release.

The comparison is defined relative to the version of the RapidIO MegaCore function

available with the Altera software release v12.1. To compare the RapidIO II MegaCore

function to previous releases of the RapidIO MegaCore function, refer to

and to the Altera documentation about the revision history of the RapidIO MegaCore

function.

f

For information about the changes in the RapidIO MegaCore function in the different

software releases, refer to the Document Revision History table in the "Additional

Information" chapter of the

nd to the "Product

Revision History" section in the RapidIO chapter

.

For information about changes to the RapidIO II MegaCore function in the different

software releases, refer to the Document Revision History table in

.

lists the major differences between these two MegaCore functions in the

12.1 software release.

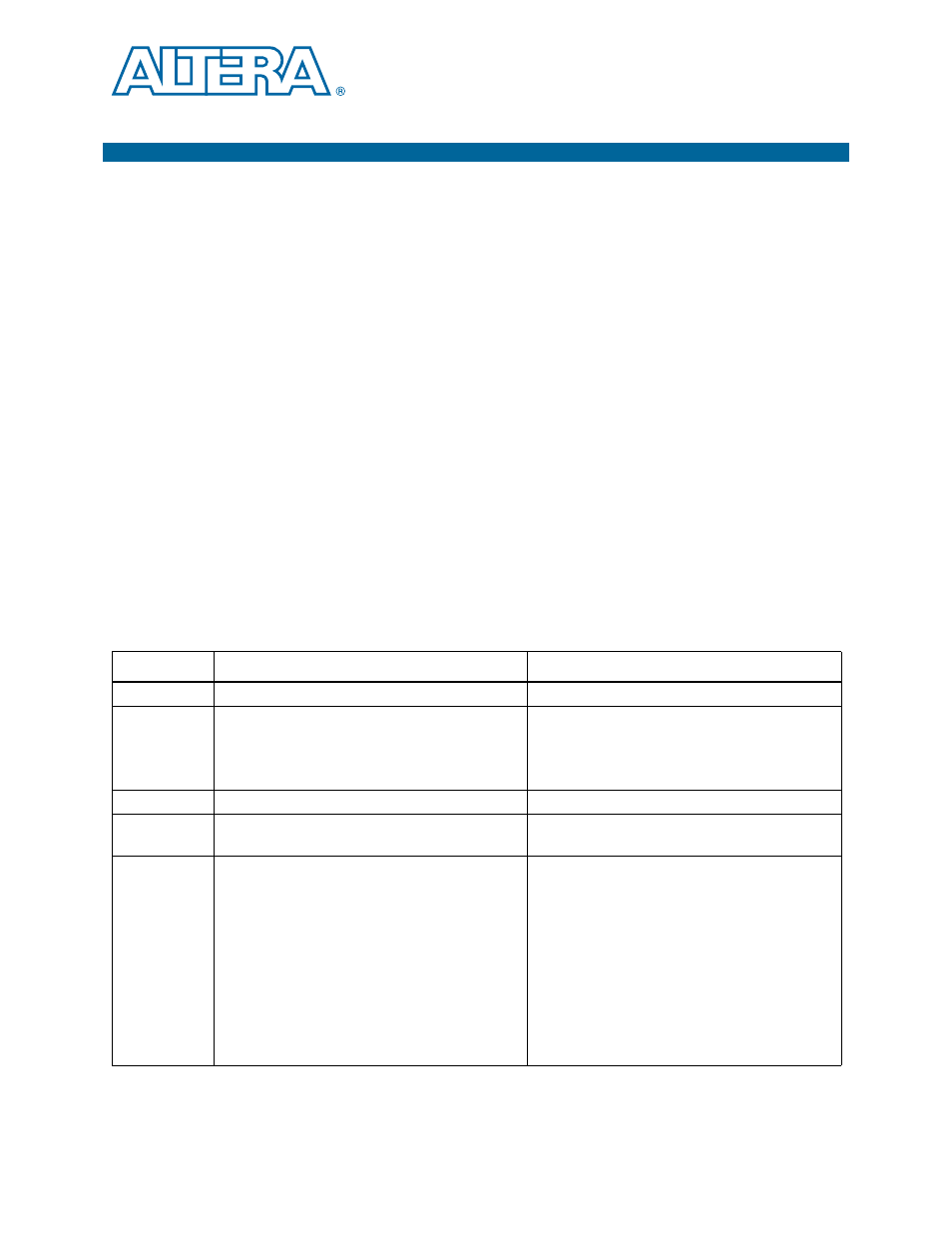

Table B–1. Major Differences Between the RapidIO II IP Core v12.1 and the RapidIO IP Core v12.1 (Part 1 of 4)

Property

RapidIO II IP Core v12.1

RapidIO IP Core v12.1

Protocol

Complies with RapidIO specification v2.2.

Complies with RapidIO specifications v1.3 and v2.1.

Device Support

Supports Arria V and Stratix V device families.

Note: Later versions add support for the Arria 10

and Cyclone V device families.

Supports multiple legacy device families, in addition

to Arria V, Cyclone V, and Stratix V device families.

Note: Later versions add support for the Arria 10

device family.

Lane support

Supports 1×, 2×, and 4× variations.

Supports 1× and 4× variations.

PHY only

Supports only variations that include a Transport

layer.

Supports Physical-layer only variations in the

MegaWizard Plug-In Manager flow.

Avalon-ST

interface width

Avalon-ST pass-through Tx interface has a 128-bit

wide interface for data; Avalon-ST pass-through Rx

interface presents data on a 128-bit wide interface

and presents packet header information on a

115-bit wide interface.

In the Rx packet header bus, the destinationID field

and the sourceID field each have 16 bits. In case of

an 8-bit device ID width, the upper 8 bits of each

field are set to all zeroes. However, in the TX

direction the destinationID and sourceID fields fit

the device ID width.

Avalon-ST pass-through Rx and Tx interfaces each

have a 32-bit wide interface in a 1× variation and a

64-bit wide interface in a 4× variation. Header and

data are transmitted or received on the same bus.

In both directions, the destinationID and sourceID

fields fit the device ID width.