Input/output slave pending transactions, Input/output slave pending transactions –41, Is set – Altera RapidIO II MegaCore Function User Manual

Page 179: Input/output slave, Table 6–61

Chapter 6: Software Interface

6–41

Transport and Logical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

Input/Output Slave Pending Transactions

INVALID_WRITE_BURSTCOUNT

[2]

RW1C

Write burst count invalid. Asserted when

io_s_burstcount

has a value that is larger than 16,

except in cases with first byteenable with a value of

0xFF00 and final byteenable with a value of 0x00FF, in an

Avalon-MM write request on the I/O Logical slave

interface. For information about valid values, refer to

1'b0

WRITE_OUT_OF_BOUNDS

[1]

RW1C

Write request address out of bounds. Asserted when the

Avalon-MM address does not fall within any enabled

address mapping window.

1'b0

READ_OUT_OF_BOUNDS

[0]

RW1C

Read request address out of bounds.

Asserted when the Avalon-MM address does not fall

within any enabled address mapping window.

1'b0

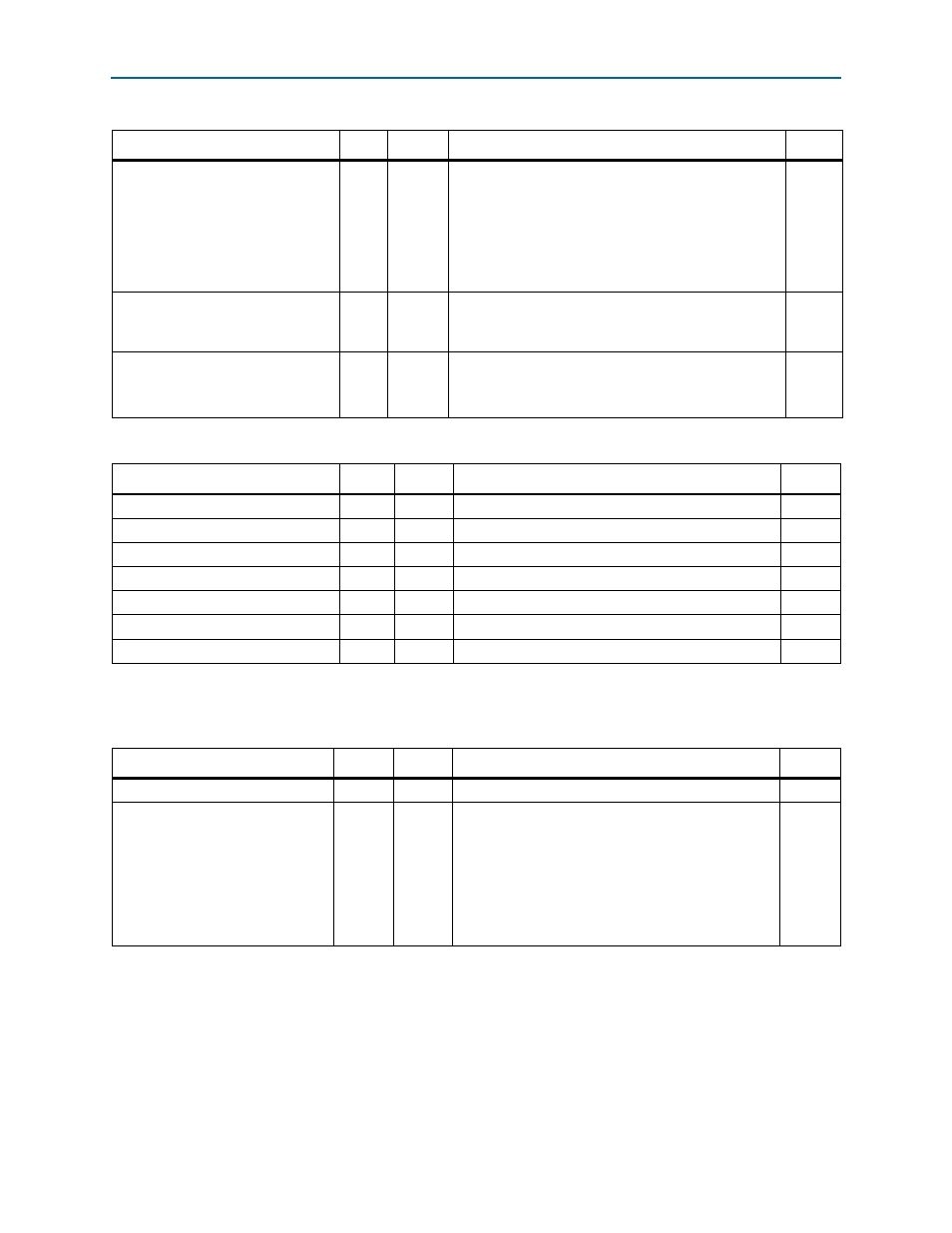

Table 6–60. Input/Output Slave Interrupt—Offset: 0x10500 (Part 2 of 2)

Field

Bits

Access

Function

Default

Table 6–61. Input/Output Slave Interrupt Enable—Offset: 0x10504

Field

Bits

Access

Function

Default

RSRV

[31:6]

RO

Reserved

26'h0

INVALID_READ_BURSTCOUNT

[5]

RW

Read burst count invalid interrupt enable

1'b0

INVALID_READ_BYTEENABLE

[4]

RW

Read byte enable invalid interrupt enable

1'b0

INVALID_WRITE_BYTEENABLE

[3]

RW

Write byte enable invalid interrupt enable

1'b0

INVALID_WRITE_BURSTCOUNT

[2]

RW

Write burst count invalid interrupt enable

1'b0

WRITE_OUT_OF_BOUNDS

[1]

RW

Write request address out of bounds interrupt enable

1'b0

READ_OUT_OF_BOUNDS

[0]

RW

Read request address out of bounds interrupt enable

1'b0

Table 6–62. Input/Output Slave Pending NWRITE_R Transactions—Offset: 0x10508

Field

Bits

Access

Function

Default

RSRV

[31:8]

RO

Reserved

24'h0

PENDING_NWRITE_RS

[7:0]

RO

Number of pending NWRITE_R write requests that

have been initiated in the I/O Avalon-MM slave Logical

layer module but have not yet completed.

The value in this field might update only after a delay

of 4 Avalon clock cycles after the start of the write

burst on the Avalon-MM interface.

8'b0